Table 5-60, Bank 5 bit map, Table 5-61 – AMD Geode SC1201 User Manual

Page 140: Bank 6 bit map, Table 5-62, Bank 7 bit map

140

AMD Geode™ SC1200/SC1201 Processor Data Book

SuperI/O Module

32579B

06h

RFRML(L)/

RFRCC(L)

RFRML[7:0] / RFRCC[7:0] (Low Byte Data)

07h

RFRML(H)/

RFRCC(H)

RSVD

RFRML[12:8] / RFRCC[12:8] (High Byte Data)

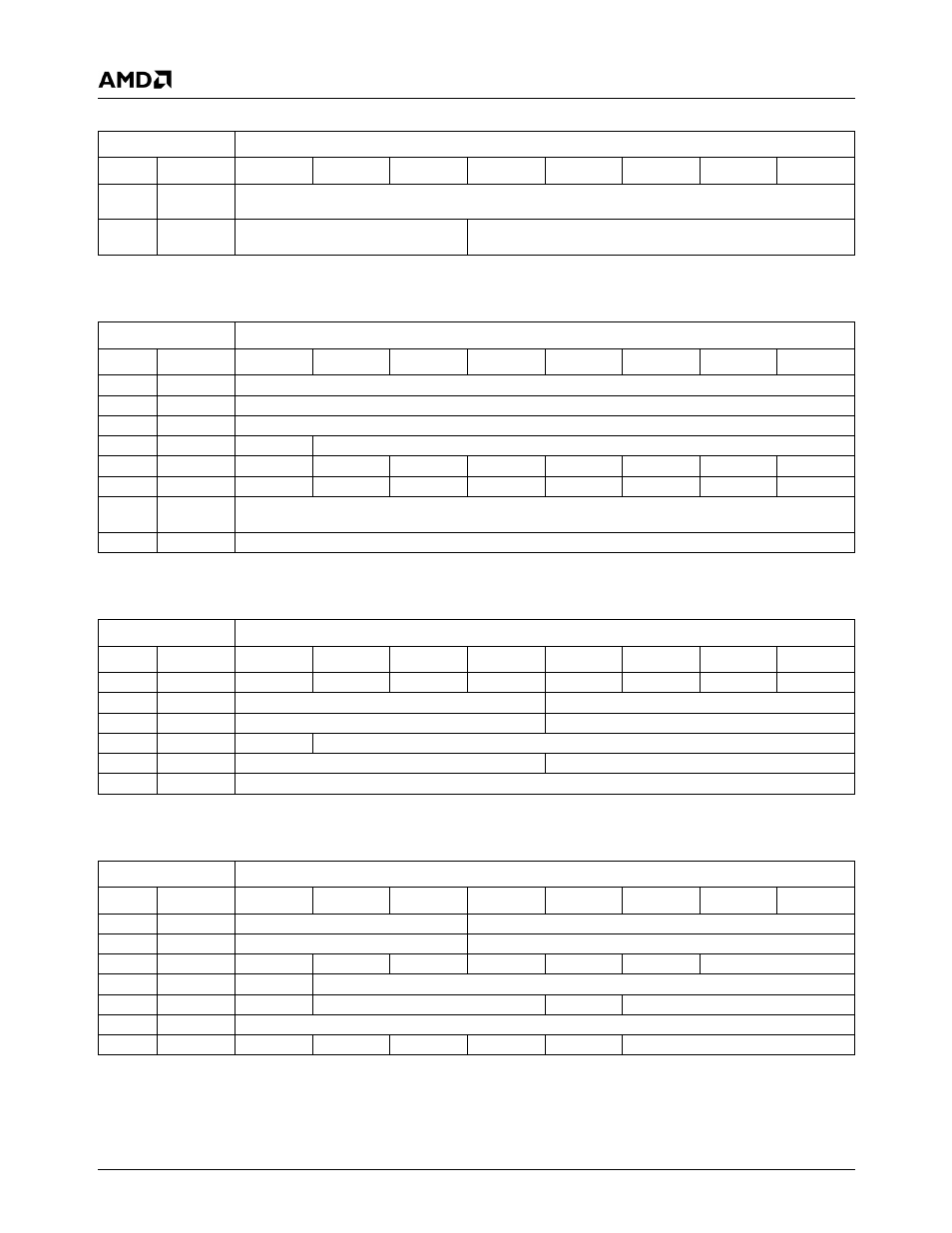

Table 5-59. Bank 4 Bit Map (Continued)

Register

Bits

Offset

Name

7

6

5

4

3

2

1

0

Table 5-60. Bank 5 Bit Map

Register

Bits

Offset

Name

7

6

5

4

3

2

1

0

00h

SPR2

Scratchpad 2

01h

SPR3

Scratchpad 2

02h

RSVD

RSVD

03h

BSR

BKSE

BSR[6:0] (Bank Select)

04h

IRCR2

RSVD

SFTSL

FEND_MD

AUX_IRRX

TX_MS

MDRS

IRMSSL

IR_FDPLX

05h

FRM_ST

VLD

LOST_FR

RSVD

MAX_LEN

PHY_ERR

BAD_CRC

OVR1

OVR2

06h

RFRL(L)/

LSTFRC

RFRL[7:0] (Low Byte Data) / LSTFRC[7:0]

07h

RFRL(H)

RFRL[15:8] (High Byte Data)

Table 5-61. Bank 6 Bit Map

Register

Bits

Offset

Name

7

6

5

4

3

2

1

0

00h

IRCR3

SHDM_DS

SHMD_DS

FIR_CRC

MIR_CRC

RSVD

TXCRC_INV TXCRC_DS

RSVD

01h

MIR_PW

RSVD

MPW[3:0]

02h

SIR_PW

RSVD

SPW[3:0]

03h

BSR

BKSE

BSR[6:0] (Bank Select)

04h

BFPL

MBF[3:0]

FPL[3:0]

05h-07h

RSVD

RSVD

Table 5-62. Bank 7 Bit Map

Register

Bits

Offset

Name

7

6

5

4

3

2

1

0

00h

IRRXDC

DBW[2:0]

DFR[4:0]

01h

IRTXMC

MCPW[2:0]

MCFR[4:0]

02h

RCCFG

R_LEN

T_OV

RXHSC

RCDM_DS

RSVD

TXHSC

RC_MMD[1:0]

03h

BSR

BKSE

BSR[6:0] (Bank Select)

04h

IRCFG1

STRV_MS

SIRC[2:0]

IRID3

IRIC[2:0]

05h-06h

RSVD

RSVD

07h

IRCFG4

RSVD

IRRX_MD

IRSL0_DS

RXINV

IRSL21_DS

RSVD