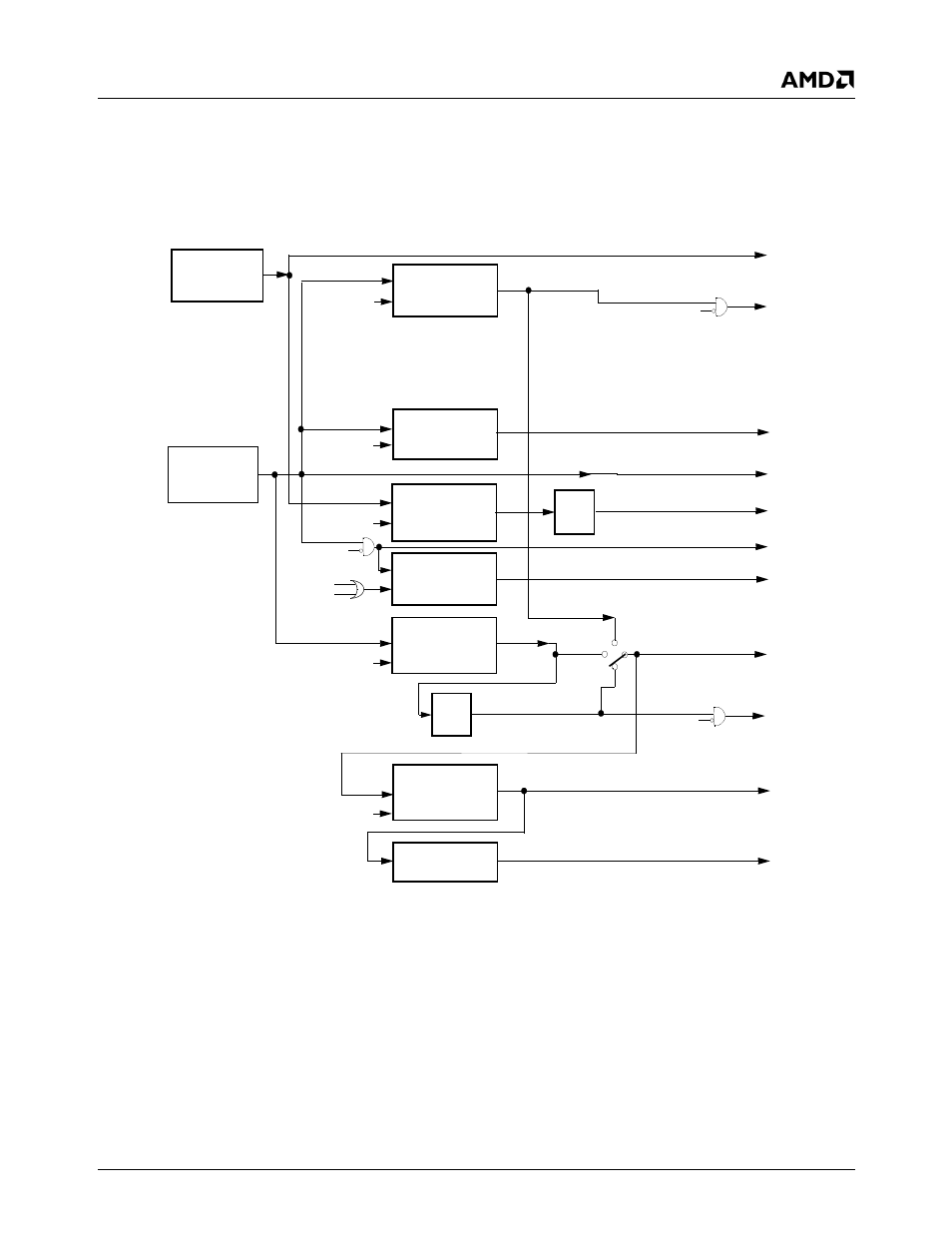

5 clock generators and plls, Clock generators and plls, Figure 4-2 – AMD Geode SC1201 User Manual

Page 83: Clock generation block diagram, In section 4.5 "clock

AMD Geode™ SC1200/SC1201 Processor Data Book

83

General Configuration Block

32579B

4.5

Clock Generators and PLLs

This section describes the registers for the clocks required

by the GX1 module, Core Logic module, and the Video

Processor, and how these clocks are generated. See Fig-

ure 4-2 for a clock generation diagram.

The clock generators are based on 32.768 KHz and 27.000

MHz crystal oscillators. The 32.768 KHz crystal oscillator is

described in Section 5.5.2 "RTC Clock Generation" on

page 105 (functional description of the RTC).

Figure 4-2. Clock Generation Block Diagram

32.768 KHz

Crystal

External PCI Clock

PLL5

Internal Fast-PCI Clock

PLL6

ACPI Clock (14.318 MHz)

PLL2

Dot Clock

Core Clock

ADL

PLL4

USB Clock (48 MHz)

Divider

SDRAM Clock

32.768 KHz

and I/O Block Clock

Real-Time Clock (RTC)

24.576 MHz

PLL3

AC97_CLK

Divide

by 4

Divide

by 2

(33.3 MHz)

48 MHz

33 MHz

66 MHz

Oscillator

(24.576 MHz)

To PAD

DISABLE

DISABLE

DISABLE

Shutdown

Shutdown

Shutdown

Shutdown

Shutdown

27 MHz

Crystal

Oscillator

CLK27M Ball

(ACPI)

(ACPI)

High-Resolution Timer Clock

Shutdown

CLK

Shutdown

48 MHz

57.273 MHz

25-135 MHz

66.67 MHz

100-333 MHz

Note:

V

PLL2

powers PLL2 and PLL5. V

PLL3

powers PLL3, PLL4, and PLL6.