AMD Geode SC1201 User Manual

Page 194

194

AMD Geode™ SC1200/SC1201 Processor Data Book

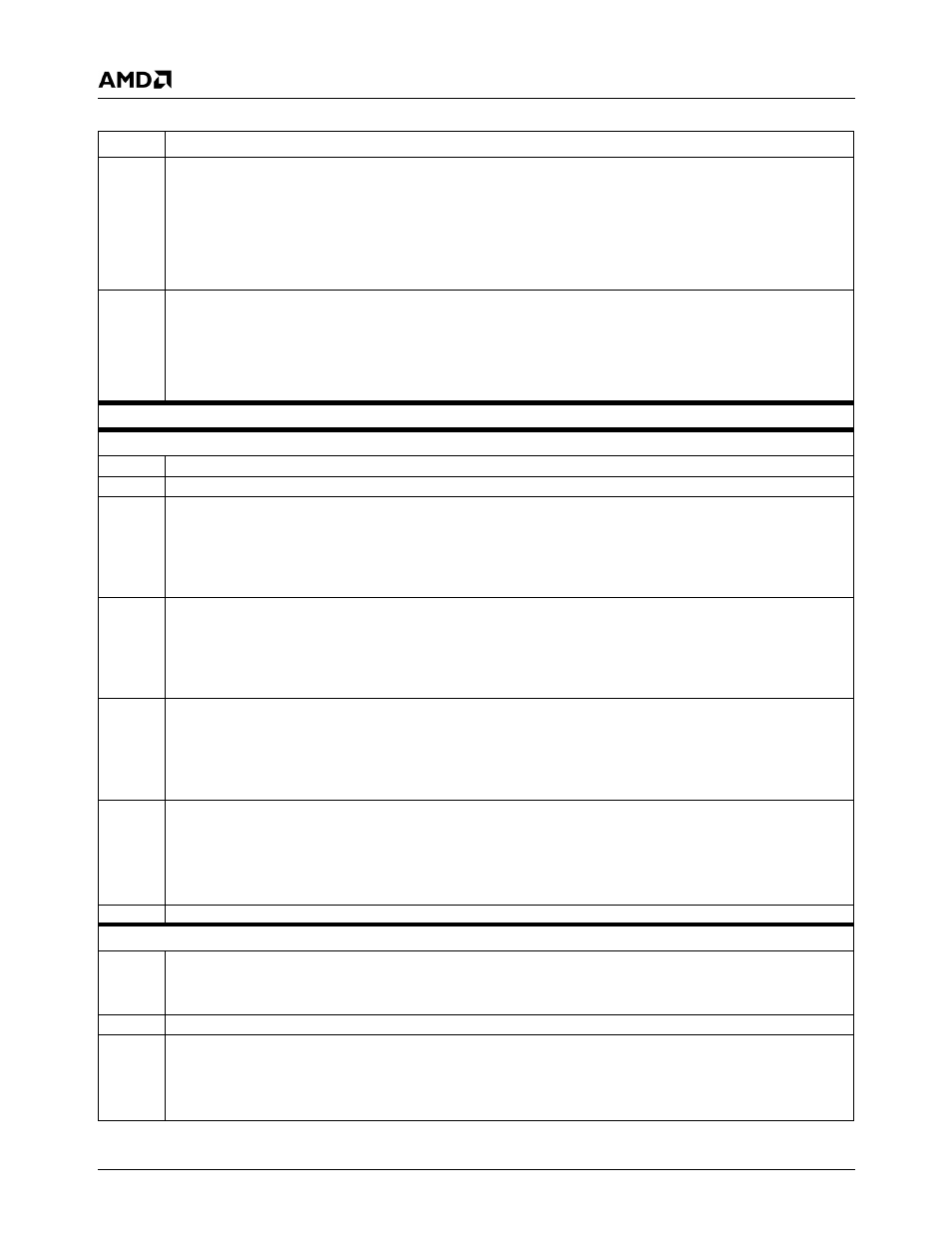

Core Logic Module - Bridge, GPIO, and LPC Registers - Function 0

32579B

1

Power Management Configuration Trap. If this bit is set to 1 and an access occurs to one of the configuration registers in

PCI Function 1 (F1) register space, an SMI is generated. Writes are trapped; access to the register is denied. Reads are

snooped; access to the register is allowed.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[9].

Second level SMI status is reported at F1BAR0+I/O Offset 04h/06h[5].

0

Legacy Configuration Trap. If this bit is set to 1 and an access occurs to one of the configuration registers in PCI Function

0 (F0), an SMI is generated. Reads and writes are snooped; access to the register is allowed.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[9].

Second level SMI status is reported at F1BAR0+I/O Offset 04h/06h[5].

Index 42h

Reserved

Reset Value: 00h

Index 43h

Delayed Transactions Register (R/W)

Reset Value: 02h

7:6

Reserved. Must be set to 0.

5

Reserved. Must be set to 1.

4

Enable PCI Delayed Transactions for Access to I/O Address 170h-177h (Secondary IDE Channel). PIO mode uses

repeated I/O transactions that are faster when non-delayed transactions are used.

0: I/O addresses complete as fast as possible on PCI. (Default)

1: Accesses to Secondary IDE channel I/O addresses are delayed transactions on PCI.

For best performance of VIP, this bit should be set to 1 unless PIO mode 3 or 4 are used.

3

Enable PCI Delayed Transactions for Access to I/O Address 1F0h-1F7h (Primary IDE Channel). PIO mode uses

repeated I/O transactions that are faster when non-delayed transactions are used.

0: I/O addresses complete as fast as possible on PCI. (Default)

1: Accesses to Primary IDE channel I/O addresses are delayed transactions on PCI.

For best performance of VIP, this bit should be set to 1 unless PIO mode 3 or 4 are used.

2

Enable PCI Delayed Transactions for AT Legacy PIC I/O Addresses. Some PIC status reads are long. Enabling delayed

transactions help reduce DMA latency for high bandwidth devices like VIP.

0: PIC I/O addresses complete as fast as possible on PCI. (Default)

1: Accesses to PIC I/O addresses are delayed transactions on PCI.

For best performance of VIP, this bit should be set to 1.

1

Enable PCI Delayed Transactions for AT Legacy PIT I/O Addresses. Some x86 programs (certain benchmarks/diagnos-

tics) assume a particular latency for PIT accesses; this bit allows that code to work.

0: PIT I/O addresses complete as fast as possible on PCI.

1: Accesses to PIT I/O addresses are delayed transactions on PCI. (Default)

For best performance (e.g., when running Microsoft

®

Windows

®

), this bit should be set to 0.

0

Reserved. Must be set to 0.

Index 44h

Reset Control Register (R/W)

Reset Value: 01h

7

AC97 Soft Reset. Active low reset for the AC97 codec interface.

0: AC97_RST# is driven high. (Default)

1: AC97_RST# is driven low.

6:4

Reserved. Must be set to 0.

3

IDE Controller Reset. Reset the IDE controller.

0: Disable.

1: Enable.

Write 0 to clear. This bit is level-sensitive and must be cleared after the reset is enabled.

Table 6-29. F0: PCI Header/Bridge Configuration Registers for GPIO and LPC Support (Continued)

Bit

Description