Table 5-35, Parallel port bit map for first level offset, Table 5-36 – AMD Geode SC1201 User Manual

Page 130: Parallel port bit map for second level offset

130

AMD Geode™ SC1200/SC1201 Processor Data Book

SuperI/O Module

32579B

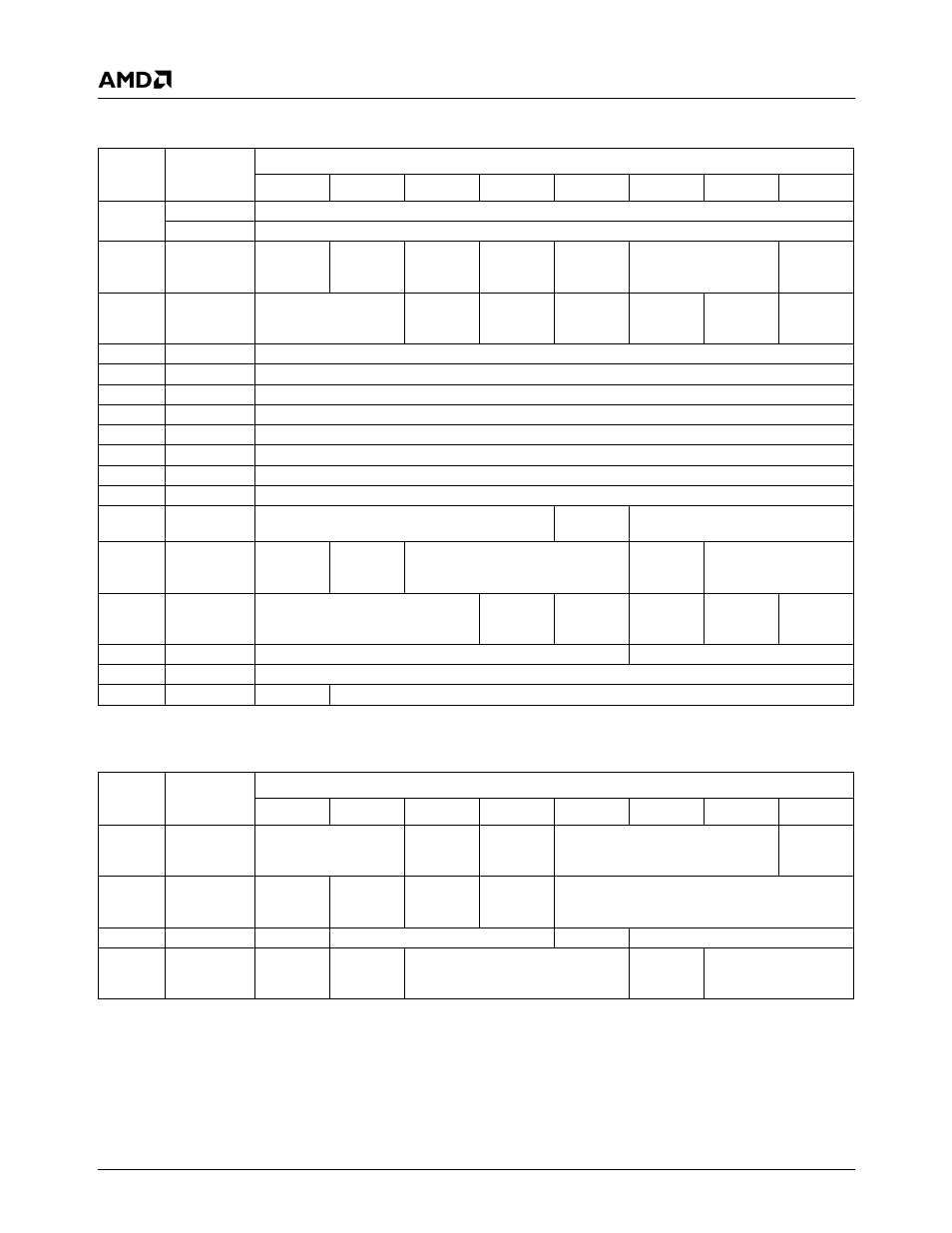

Table 5-35. Parallel Port Bit Map for First Level Offset

Offset

Name

Bits

7

6

5

4

3

2

1

0

000h

DATAR

Data Bits

AFIFO

Address Bits

001h

DSR

Printer

Status

ACK#

Status

PE

Status

SLCT

Status

ERR#

Status

RSVD

EPP

Timeout

Status

002h

DCR

RSVD

Direction

Control

Interrupt

Enable

PP Input

Control

Printer Ini-

tialization

Control

Automatic

Line Feed

Control

Data

Strobe

Control

003h

ADDR

EPP Device or Register Selection Address Bits

004h

DATA0

EPP Device or R/W Data

005h

DATA1

EPP Device or R/W Data

006h

DATA2

EPP Device or R/W Data

007h

DATA3

EPP Device or R/W Data

400h

CFIFO

Data Bits

400h

DFIFO

Data Bits

400h

TFIFO

Data Bits

400h

CNFGA

RSVD

Bit 7 of PP

Confg0

RSVD

401h

CNFGB

RSVD

Interrupt

Request

Value

Interrupt Select

RSVD

DMA Channel Select

402h

ECR

ECP Mode Control

ECP Inter-

rupt Mask

ECP DMA

Enable

ECP Inter-

rupt Ser-

vice

FIFO

Full

FIFO

Empty

403h

EIR

RSVD

Second Level Offset

404h

EDR

Data Bits

405h

EAR

FIFO Tag

RSVD

Table 5-36. Parallel Port Bit Map for Second Level Offset

Offset

Name

Bits

7

6

5

4

3

2

1

0

00h

Control0

RSVD

DCR Reg-

ister Live

Freeze Bit

RSVD

EPP Time-

out Inter-

rupt Mask

02h

Control2

SPP Com-

patibility

Channel

Address

Enable

RSVD

Revision

1.7 or 1.9

Select

RSVD

04h

Control4

RSVD

PP DMA Request Inactive Time

RSVD

PP DMA Request Active Time

05h

PP Confg0

Bit 3 of

CNFGA

Demand

DMA

Enable

ECP IRQ Channel Number

PE Inter-

nal PU or

PD

ECP DMA Channel

Number