AMD Geode SC1201 User Manual

Page 127

AMD Geode™ SC1200/SC1201 Processor Data Book

127

SuperI/O Module

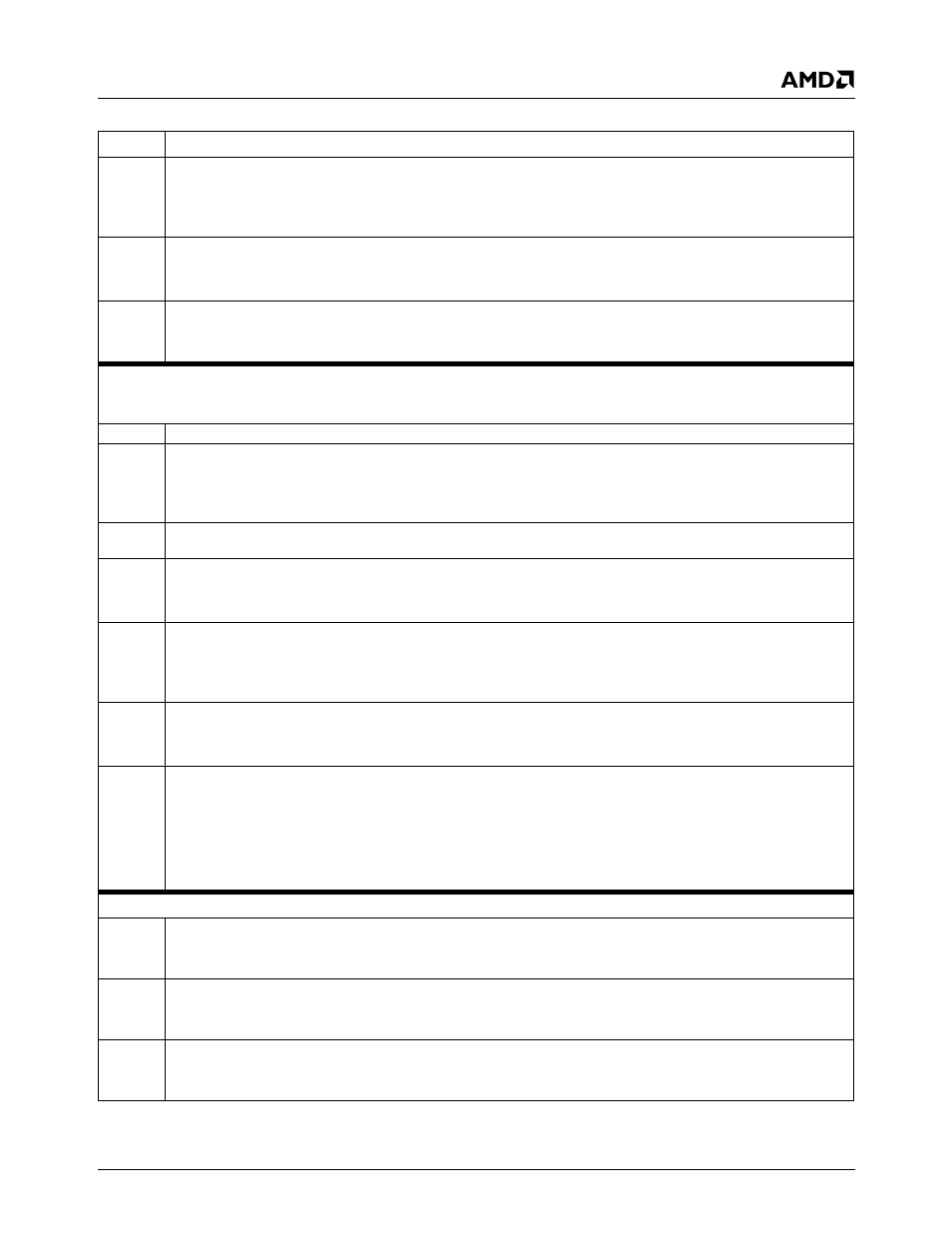

32579B

2

NMATCH (New Match). (R/W1C) Writing 0 to this bit is ignored. If ACBCTL1[2] is set, an interrupt is sent when this bit is

set.

0: Software writes 1 to this bit.

1: Address byte follows a Start Condition or a repeated start, causing a match or a global-call match.

1

MASTER. (RO)

0: Arbitration loss (BER, bit 5, is set) or recognition of a Stop Condition.

1: Bus master request succeeded and master mode active.

0

XMIT (Transmit). (RO) Direction bit.

0: Master/slave transmit mode not active.

1: Master/slave transmit mode active.

Offset 02h

ACB Control Status Register - ACBCST (R/W)

Reset Value: 00h

This register configures and controls the ACB functional block. It maintains the current ACB status and controls several ACB functions.

On reset and when the ACB is disabled, the non-reserved bits of ACBCST are cleared.

7:6

Reserved.

5

TGABC (Toggle ABC Line). (R/W) Enables toggling the ABC line during error recovery.

0: Clock toggle completed.

1: When the ABD line is low, writing 1 to this bit toggles the ABC line for one cycle. Writing 1 to TGABC while ABD is high

is ignored.

4

TSDA (Test ABD Line). (RO) Reads the current value of the ABD line. It can be used while recovering from an error condi-

tion in which the ABD line is constantly pulled low by an out-of-sync slave. Data written to this bit is ignored.

3

GCMTCH (Global Call Match). (RO)

0: Start Condition or repeated Start and a Stop Condition (including illegal Start or Stop Condition).

1: In slave mode, ACBCTL1.GCMEN is set and the address byte (the first byte transferred after a Start Condition) is 00h.

2

MATCH (Address Match). (RO)

0: Start Condition or repeated Start and a Stop Condition (including illegal Start or Stop Condition).

1: ACBADDR[7] is set and the first 7 bits of the address byte (the first byte transferred after a Start Condition) match the 7-

bit address in ACBADDR.

1

BB (Bus Busy). (R/W1C)

0: Writing 1, ACB disabled, or Stop Condition detected.

1: Bus active (a low level on either ABD or ABC), or Start Condition.

0

BUSY. (RO) This bit should always be written 0. This bit indicates the period between detecting a Start Condition and com-

pleting receipt of the address byte. After this, the ACB is either free or enters slave mode.

0: Completion of any state below or ACB disabled.

1: ACB is in one of the following states:

-Generating a Start Condition

-Master mode (ACBST[1] is set)

-Slave mode (ACBCST[2] or ACBCST[3] set).

Offset 03h

ACB Control Register 1 - ACBCTL1 (R/W)

Reset Value: 00h

7

STASTRE (Stall After Start Enable).

0: When cleared, ACBST[3] can not be set. However, if ACBST[3] is set, clearing STASTRE does not clear ACBST[3].

1: Stall after start mechanism enabled, and ACB stalls the bus after the address byte.

6

NMINTE (New Match Interrupt Enable).

0: No interrupt issued on a new match.

1: Interrupt issued on a new match only if ACBCTL1[2] set.

5

GCMEN (Global Call Match Enable).

0: Global call match disabled.

1: Global call match enabled.

Table 5-32. ACB Registers (Continued)

Bit

Description