2 lpc support registers, Table 6-31, Table 6-31) – AMD Geode SC1201 User Manual

Page 228

228

AMD Geode™ SC1200/SC1201 Processor Data Book

Core Logic Module - Bridge, GPIO, and LPC Registers - Function 0

32579B

6.4.1.2

LPC Support Registers

F0 Index 14h, Base Address Register 1 (F0BAR1) points to

the base address of the register space that contains the

configuration registers for LPC support. Table 6-31 gives

the bit formats of the I/O mapped registers accessed

through F0BAR1.

The LPC Interface supports all features described in the

LPC bus specification 1.0, with the following exceptions:

• Only 8- or 16-bit DMA, depending on channel number.

Does not support the optional larger transfer sizes.

• Only one external DRQ pin.

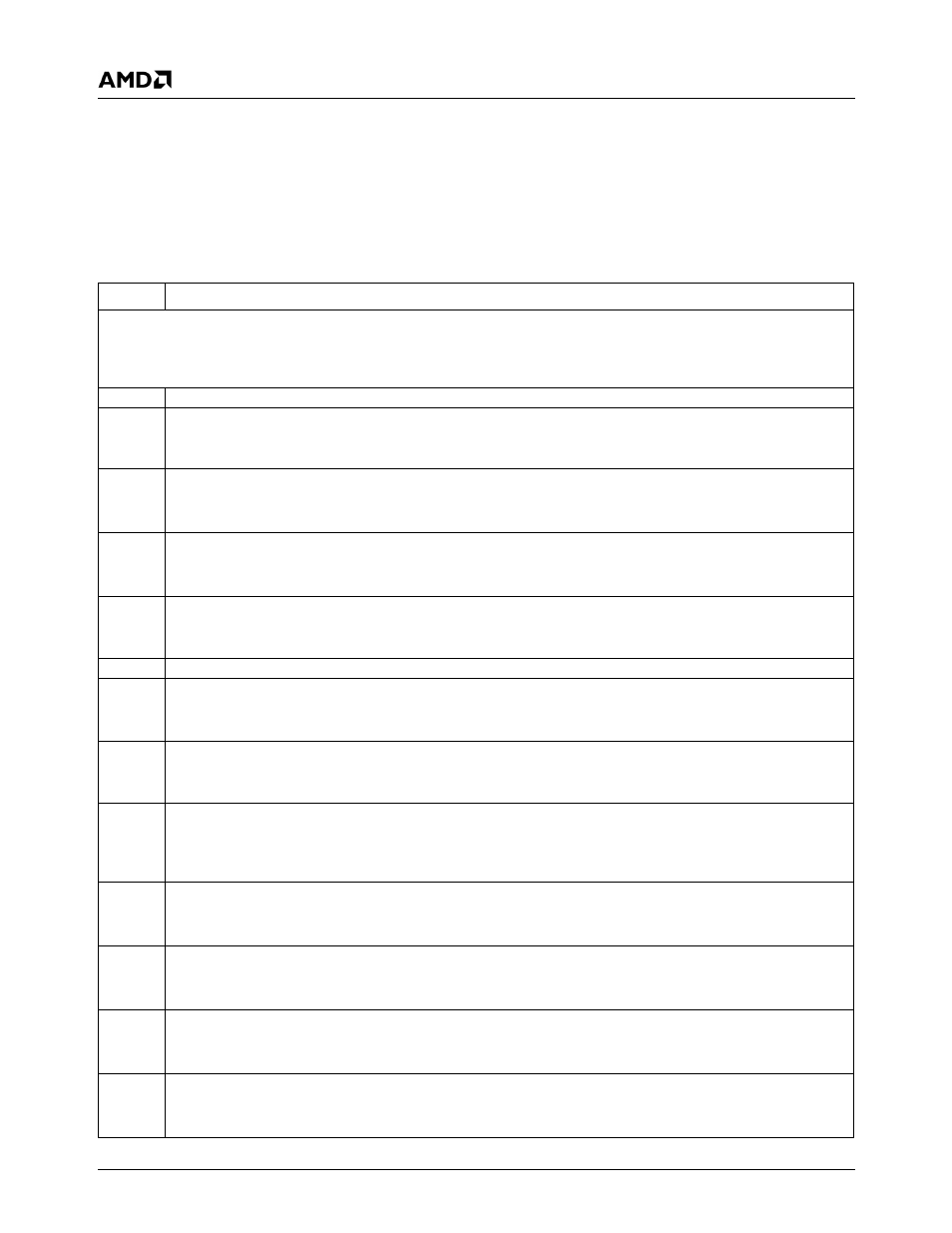

Table 6-31. F0BAR1+I/O Offset: LPC Interface Configuration Registers

Bit

Description

Offset 00h-03h

SERIRQ_SRC — Serial IRQ Source Register (R/W)

Reset Value: 00000000h

Note:

Some signals require additional programming to make them externally accessible. See Table 4-2 "Pin Multiplexing, Interrupt

Selection, and Base Address Registers" on page 72 for pin multiplexing details and Table 3-4 "Strap Options" on page 44 for

LPC_ROM strap information.

31:21

Reserved.

20

INTD Source. Selects the interface source of the INTD# signal.

0: PCI - INTD# (ball AA2).

1: LPC - SERIRQ (ball J31).

19

INTC Source. Selects the interface source of the INTC# signal.

0: PCI - INTC# (ball C9).

1: LPC - SERIRQ (ball J31).

18

INTB Source. Selects the interface source of the INTB# signal.

0: PCI - INTB# (ball C26).

1: LPC - SERIRQ (ball J31).

17

INTA Source. Selects the interface source of the INTA# signal.

0: PCI - INTA# (ball D26).

1: LPC - SERIRQ (ball J31).

16

Reserved. Set to 0.

15

IRQ15 Source. Selects the interface source of the IRQ15 signal.

0: ISA - IRQ15 (ball AJ8).

1: LPC - SERIRQ (ball J31).

14

IRQ14 Source. Selects the interface source of the IRQ14 signal.

0: ISA - IRQ14 (ball AF1).

1: LPC - SERIRQ (ball J31).

13

IRQ13 Source. Selects the interface source of the internal IRQ13 signal.

0: ISA - IRQ13 internal signal. (An input from the CPU indicating that a floating point error has been detected and that inter-

nal INTR should be asserted.)

1: LPC - SERIRQ (ball J31).

12

IRQ12 Source. Selects the interface source of the IRQ12 signal.

0: ISA - IRQ12 (unavailable externally).

1: LPC - SERIRQ (ball J31).

11

IRQ11 Source. Selects the interface source of the IRQ11 signal.

0: ISA - IRQ11 (unavailable externally).

1: LPC - SERIRQ (ball J31).

10

IRQ10 Source. Selects the interface source of the IRQ10 signal.

0: ISA - IRQ10 (unavailable externally).

1: LPC - SERIRQ (ball J31).

9

IRQ9 Source. Selects the interface source of the IRQ9 signal.

0: ISA - IRQ9 (ball AA3).

1: LPC - SERIRQ (ball J31).