6 lpc interface signal definitions, 7 cycle types, 8 lpc interface support – AMD Geode SC1201 User Manual

Page 174: Table 6-12, Cycle types

174

AMD Geode™ SC1200/SC1201 Processor Data Book

Core Logic Module

32579B

6.2.12.6 LPC Interface Signal Definitions

The LPC specification lists seven required and six optional

signals for supporting the LPC interface. Many of the sig-

nals are the same signals found on the PCI interface and

do not require any new pins on the host. Required signals

must be implemented by both hosts and peripherals.

Optional signals may or may not be present on particular

hosts or peripherals.

The Core Logic module incorporates all the required LPC

interface signals and two of the optional signals:

• Required LPC signals:

— LAD[3:0] - Multiplexed Command, Address and Data.

— LFRAME# - Frame: Indicates start of a new cycle,

termination of broken cycle.

— LRESET# - Reset: This signal is not available. Use

PCI Reset signal PCIRST# instead.

— LCLK - Clock: This signal is not available. Use PCI 33

MHz clock signal PCICLK instead.

• Core Logic module optional LPC signals:

— LDRQ# - Encoded DMA/Bus Master Request: Only

needed by peripheral that need DMA or bus

mastering. Peripherals may not share the LDRQ#

signal.

— SERIRQ - Serialized IRQ: Only needed by periph-

erals that need interrupt support.

— LPCPD# - Power Down: Indicates that the peripheral

should prepare for power to the LPC interface to be

shut down. Optional for the host.

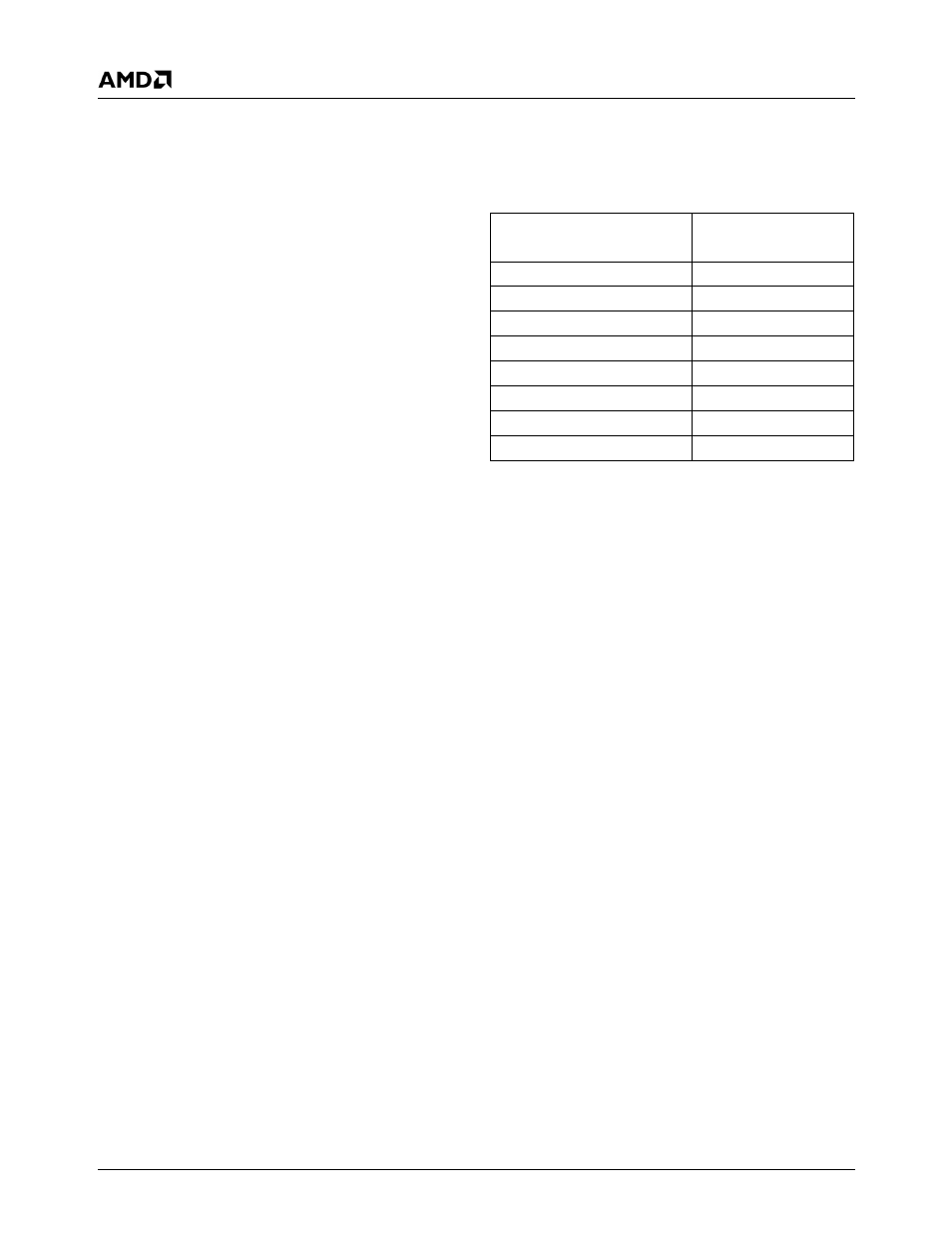

6.2.12.7 Cycle Types

Table 6-12 shows the various types of cycles that are sup-

ported by the Core Logic module.

6.2.12.8 LPC Interface Support

The LPC interface supports all the features described in

the LPC Bus Interface specification, revision 1.0, with the

following exceptions:

• Only 8- or 16-bit DMA, depending on channel number.

Does not support the optional larger transfer sizes.

• Only one external DRQ pin.

Table 6-12. Cycle Types

Cycle Type

Supported Sizes

(Bytes)

Memory Read

1

Memory Write

1

I/O Read

1

I/O Write

1

DMA Read

1 or 2

DMA Write

1 or 2

Bus Master Memory Read

1, 2, or 4

Bus Master Memory Write

1, 2, or 4