Figure 9-50, Ac97 clocks diagram, Table 9-40 – AMD Geode SC1201 User Manual

Page 428: Ac97 clocks parameters

428

AMD Geode™ SC1200/SC1201 Processor Data Book

Electrical Specifications

32579B

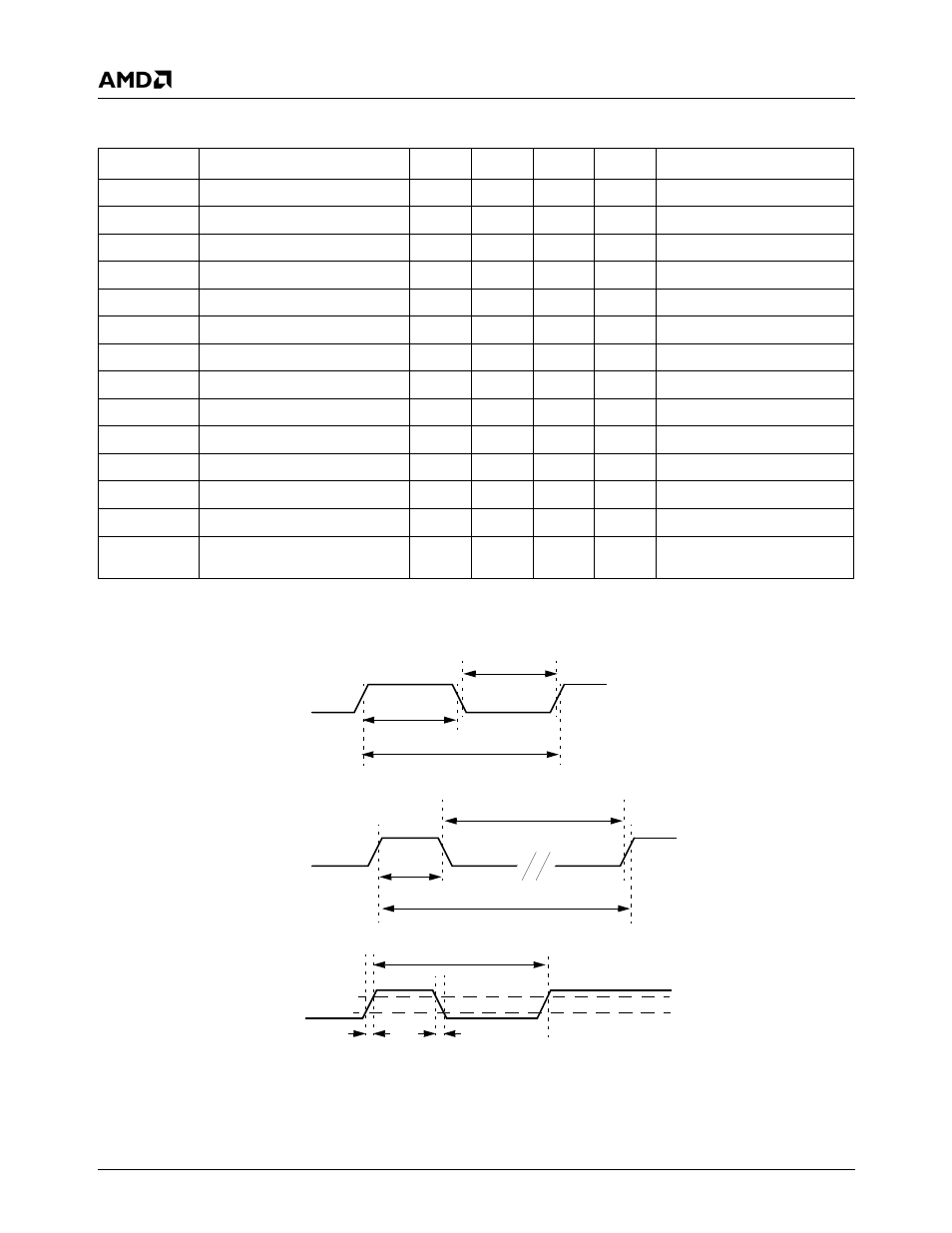

Figure 9-50. AC97 Clocks Diagram

Table 9-40. AC97 Clocks Parameters

Symbol

Parameter

Min

Typ

Max

Unit

Comments

F

BIT_CLK

BIT_CLK frequency

12.288

MHz

t

CLK_PD

BIT_CLK period

81.4

ns

t

CLK_J

BIT_CLK output jitter

750

ps

t

CLK_H

BIT_CLK high pulse width

32.56

40.7

48.84

ns

Note 1

t

CLK_L

BIT_CLK low pulse width

32.56

40.7

48.84

ns

Note 1

F

SYNC

SYNC frequency

48.0

KHz

t

SYNC_PD

SYNC period

20.8

µs

t

SYNC_H

SYNC high pulse width

1.3

µs

t

SYNC_L

SYNC low pulse width

19.5

µs

F

AC97_CLK

AC97_CLK frequency

24.576

MHz

t

AC97_CLK_PD

AC97_CLK period

40.7

ns

t

AC97_CLK_D

AC97_CLK duty cycle

45

55

%

t

AC97_CLK_FR

AC97_CLK fall/rise time

2

5

ns

t

AC97_CLK_J

AC97_CLK output edge-to-

edge jitter

100

ps

Measured from edge to edge

Note 1. Worst case duty cycle restricted to 40/60.

BIT_CLK

SYNC

t

CLK_PD

t

CLK_H

t

CLK_L

t

SYNC_H

t

SYNC_L

t

SYNC_PD

t

AC97_CLK_FR

V

OHD

V

OLD

t

AC97_CLK_PD

AC97_CLK