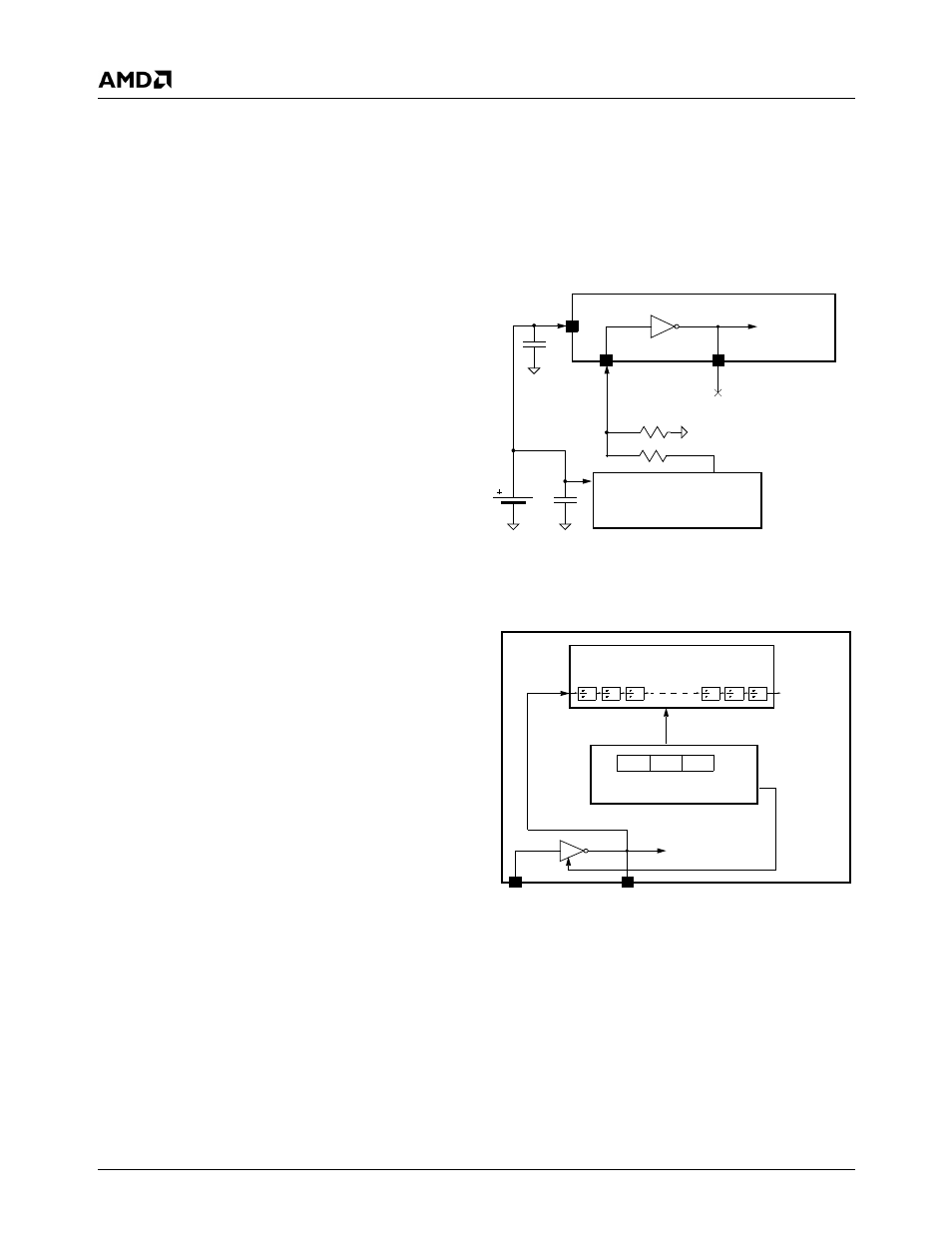

2 external oscillator, 3 timing generation, Figure 5-6 – AMD Geode SC1201 User Manual

Page 106: External oscillator connections, Figure 5-7, Divider chain control

106

AMD Geode™ SC1200/SC1201 Processor Data Book

SuperI/O Module

32579B

External Elements

Choose C

1

and C

2

capacitors (see Figure 5-5 on page

105) to match the crystal’s load capacitance. The load

capacitance C

L

“seen” by crystal Y is comprised of C

1

in

series with C

2

and in parallel with the parasitic capacitance

of the circuit. The parasitic capacitance is caused by the

chip package, board layout and socket (if any), and can

vary from 0 to 10 pF. The rule of thumb in choosing these

capacitors is:

C

L

= (C

1

* C

2

) / (C

1

+ C

2

) + C

PARASITIC

Example:

Crystal C

L

= 10 pF, C

PARASITIC

= 8.2 pF

C

1

= 3.6 pF, C

2

= 3.6 pF

Oscillator Startup

The oscillator starts to generate 32.768 KHz pulses to the

RTC after about 100 msec from when V

BAT

is higher than

V

BATMIN

(2.4V) or V

SB

is higher than V

SBMIN

(3.0V). The

oscillation amplitude on the X32O pin stabilizes to its final

value (approximately 0.4V peak-to-peak around 0.7V DC)

in about 1 s.

C

1

can be trimmed to achieve precisely 32.768 KHz. To

achieve a high time accuracy, use crystal and capacitors

with low tolerance and temperature coefficients.

5.5.2.2

External Oscillator

32.768 KHz can be applied from an external clock source,

as shown in Figure 5-6.

Connections

Connect the clock to the X32I ball, leaving the oscillator

output, X32O, unconnected.

Signal Parameters

The signal levels should conform to the voltage level

requirements for X32I, of square or sine wave of 0.0V to

V

CORE

amplitude. The signal should have a duty cycle of

approximately 50%. It should be sourced from a battery-

backed source in order to oscillate during power-down.

This assures that the RTC delivers updated time/calendar

information.

5.5.2.3

Timing Generation

The timing generation function divides the 32.768 KHz

clock by 2

15

to derive a 1 Hz signal, which serves as the

input for the seconds counter. This is performed by a

divider chain composed of 15 divide-by-two latches, as

shown in Figure 5-7.

Bits [6:4] (DV[2:0]) of the CRA Register control the follow-

ing functions:

• Normal operation of the divider chain (counting).

• Divider chain reset to 0.

• Oscillator activity when only V

BAT

power is present

(backup state).

The divider chain can be activated by setting normal opera-

tional mode (bits [6:4] of CRA = 01x or 100). The first

update occurs 500 msec after divider chain activation.

Bits [3:0] of CRA select one the of fifteen taps from the

divider chain to be used as a periodic interrupt. The peri-

odic flag becomes active after half of the programmed

period has elapsed, following divider chain activation.

See Table 5-20 on page 111 for more details.

Figure 5-6. External Oscillator Connections

Figure 5-7. Divider Chain Control

32.768 KHz

Clock Generator

Internal

External

CLKIN

X32O

NC

To other

modules

Battery

V

BAT

B

1

C

F

C

F

OUT

POWER

C

F

= 0.1

μF

(X32I)

R

1

R

2

R

2

= 30 K

Ω

R

1

= 30 K

Ω

3.3V square wave

32.768 KHz

2

1

2

2

2

3

2

13

2

14

2

15

1 Hz

Divider Chain

DV2 DV1 DV0

CRA Register

Oscillator

Enable

X32I

X32O

To other

Reset

6

5

4

modules