AMD Geode SC1201 User Manual

Page 253

AMD Geode™ SC1200/SC1201 Processor Data Book

253

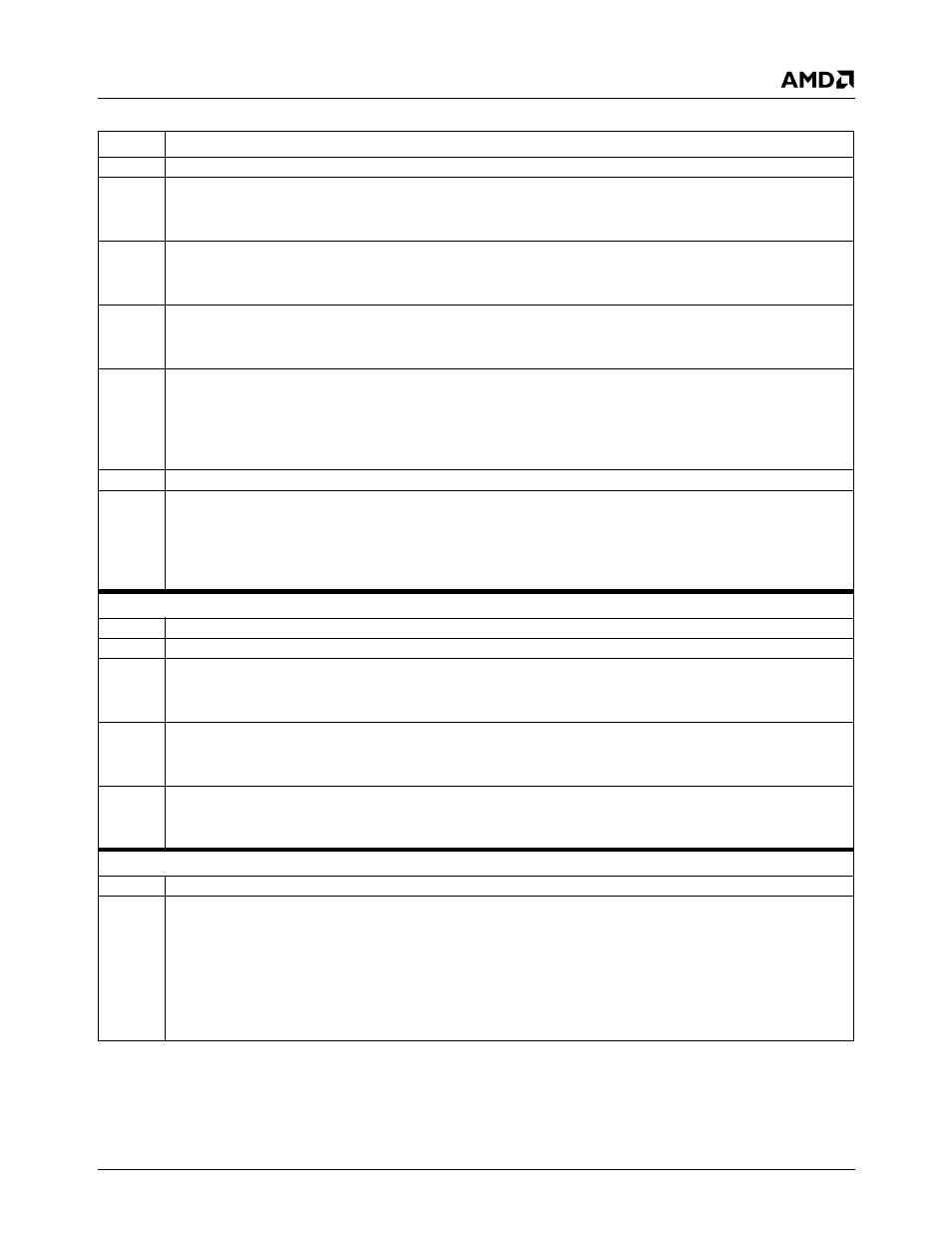

Core Logic Module - SMI Status and ACPI Registers - Function 1

32579B

7

Reserved. Must be set to 0

6

USB_EN. Allow USB events to generate a SCI.

0: Disable.

1: Enable

5

THRM_EN. Allow THRM# to generate an SCI.

0: Disable.

1: Enable

4

SMI_EN. Allow SMI events to generate an SCI.

0: Disable.

1: Enable

3

GPIO_EN. Allow GPIOs (GPIO47-GPIO32 and GPIO15-GPIO0) to generate an SCI.

0: Disable.

1: Enable.

F0BAR0+I/O Offset 08h/18h selects which GPIOs are enabled for PME generation. This bit (GPIO_EN) globally enables

those selected GPIOs for generation of an SCI.

2:1

Reserved. Must be set to 0.

0

PWR_U_REQ_EN. Allow power-up request events from the SuperI/O module to generate an SCI.

0: Disable.

1: Enable.

A power-up request event is defined as any of the following events/activities: Modem, Telephone, Keyboard, Mouse, CEIR

(Consumer Electronic Infrared)

Offset 14h

GPWIO Control Register 1 (R/W)

Reset Value: 00h

7:4

Reserved. Must be set to 0.

3

Reserved.

2

GPWIO2_POL. Select GPWIO2 polarity.

0: Active high

1: Active low

1

GPWIO1_POL. Select GPWIO1 polarity.

0: Active high

1: Active low

0

GPWIO0_POL. Select GPWIO0 polarity.

0: Active high

1: Active low

Offset 15h

GPWIO Control Register 2 (R/W)

Reset Value: 00h

7

Reserved.

6

GPWIO_SMIEN2. Allow GPWIO2 to generate an SMI.

0: Disable. (Default)

1: Enable.

A fixed high-to-low or low-to-high transition (debounce period) of 31 µs exists in order for GPWIO2 to be recognized.

Bit 2 of this register must be set to 0 (input) for GPWIO2 to be able to generate an SMI.

If asserted, this bit overrides the setting of F1BAR1+I/O Offset 12h[10] and its status is reported in F1BAR0+I/O Offset 00h/

02h[0].

Table 6-34. F1BAR1+I/O Offset: ACPI Support Registers (Continued)

Bit

Description