Transmit side d4 timing figure 15–6, Transmit side timing figure 15–7 – Rainbow Electronics DS2152 User Manual

Page 63

DS2152

031897 63/79

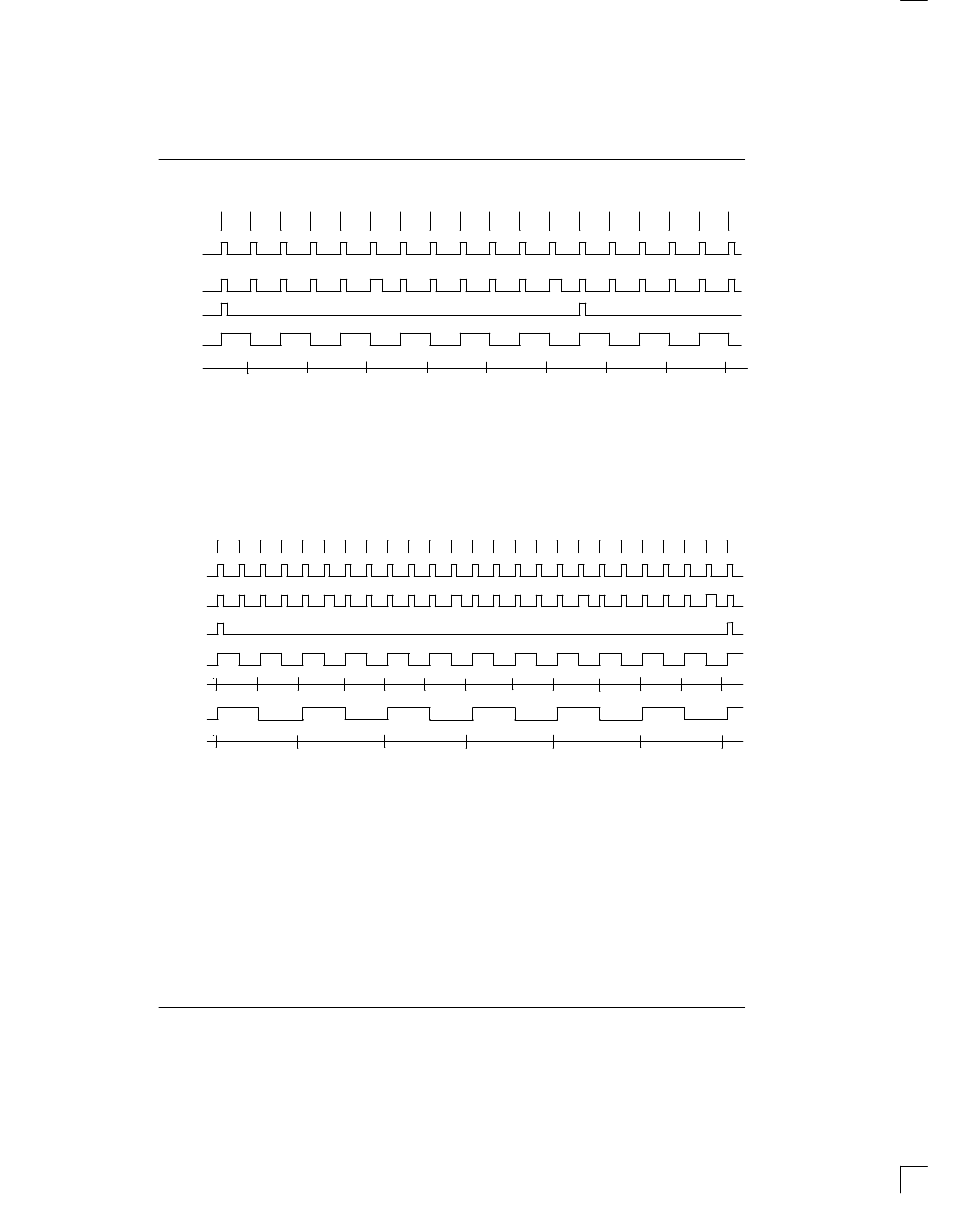

TRANSMIT SIDE D4 TIMING Figure 15–6

1

FRAME#

TSYNC

1

/

TFSYNC

TSYNC

2

TSYNC

3

TLCLK

RCHBLK

4

2

3

4

5

6

7

8

9

10

11

12

1

2

3

4

5

NOTES:

1. TSYNC in the frame mode (TCR2.3=0) and double–wide frame sync is not enabled (TCR2.4=0).

2. TSYNC in the frame mode (TCR2.3=0) and double–wide frame sync is enabled (TCR2.4=1).

3. TSYNC in the multiframe mode (TCR2.3=1).

4. TLINK data (Fs bits) is sampled during the F–bit position of even frames for insertion into the outgoing T1 stream

when enabled via TCR1.2.

5. TLINK and TLCLK are not synchronous with TFSYNC.

TRANSMIT SIDE TIMING Figure 15–7

1

FRAME#

TSYNC

1

/

TFSYNC

TSYNC

2

TSYNC

3

TLCLK

4

TLINK

TLCLK

6

TLINK

7

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

NOTES:

1. TSYNC in the frame mode (TCR2.3=0) and double–wide frame sync is not enabled (TCR2.4=0).

2. TSYNC in the frame mode (TCR2.3=0) and double–wide frame sync is enabled (TCR2.4=1).

3. TSYNC in the multiframe mode (TCR2.3=1).

4. ZBTSI mode disabled (TCR2.5=0).

5. TLINK data (FDL bits) is sampled during the F–bit time of odd frame and inserted into the outgoing T1 stream if

enabled via TCR1.2.

6. ZBTSI mode is enabled (TCR2.5=1).

7. TLINK data (Z bits) is sampled during the F–bit time of frames 1, 5, 9, 13, 17, and 21 and inserted into the outgoing

stream if enabled via TCR1.2.

8. TLINK and TLCLK are not synchronous with TFSYNC.