Rainbow Electronics DS2152 User Manual

Page 57

DS2152

031897 57/79

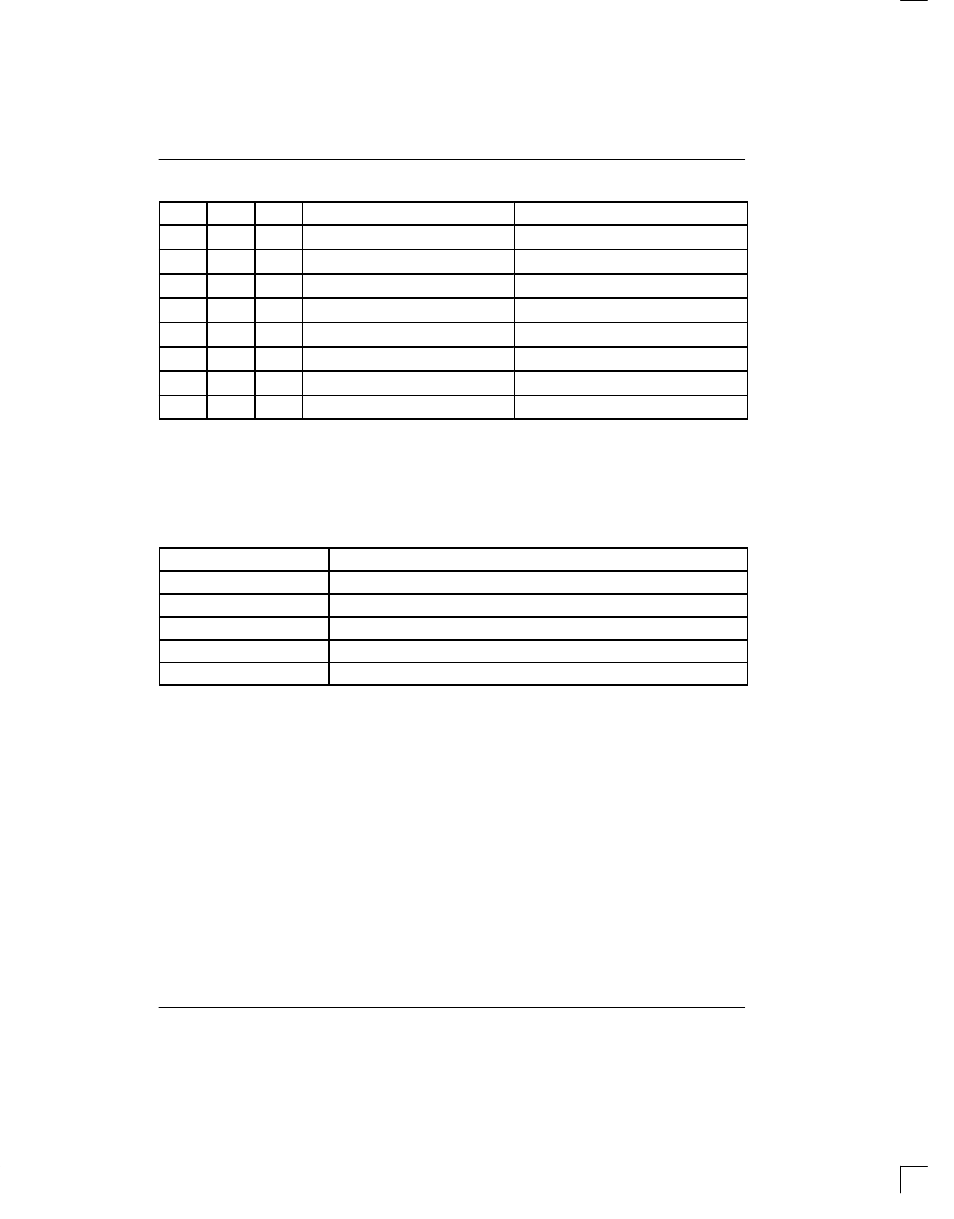

LINE BUILD OUT SELECT IN LICR Table 14.2

L2

L1

L0

LINE BUILD OUT

APPLICATION

0

0

0

0 to 133 feet / 0dB

DSX–1 / CSU

0

0

1

133 to 266 feet

DSX–1

0

1

0

266 to 399 feet

DSX–1

0

1

1

399 to 533 feet

DSX–1

1

0

0

533 to 655 feet

DSX–1

1

0

1

–7.5 dB

CSU

1

1

0

–15 dB

CSU

1

1

1

–22.5 dB

CSU

Due to the nature of the design of the transmitter in the

DS2152, very little jitter (less then 0.005 UIpp broad-

band from 10 Hz to 100 KHz) is added to the jitter pres-

ent on TCLKI. Also, the waveforms that they create are

independent of the duty cycle of TCLK. The transmitter

in the DS2152 couples to the T1 transmit twisted pair via

a 1:1.15 or 1:1.36 step up transformer as shown in

Figure 14–1. In order for the devices to create the

proper waveforms, this transformer used must meet the

specifications listed in Table 14–3.

TRANSFORMER SPECIFICATIONS Table 14–3

SPECIFICATION

RECOMMENDED VALUE

Turns Ratio

1:1 (receive) and 1:1.15 or 1:1.36 (transmit)

±

5%

Primary Inductance

600 uH minimum

Leakage Inductance

1.0 uH maximum

Intertwining Capacitance

40 pF maximum

DC Resistance

1.2 Ohms maximum

14.3 JITTER ATTENUATOR

The DS2152 contains an onboard jitter attenuator that

can be set to a depth of either 32 or 128 bits via the

JABDS bit in the Line Interface Control Register (LICR).

The 128 bit mode is used in applications where large

excursions of wander are expected. The 32 bit mode is

used in delay sensitive applications. The characteris-

tics of the attenuation are shown in Figure 14–4. The jit-

ter attenuator can be placed in either the receive path or

the transmit path by appropriately setting or clearing the

JAS bit in the LICR. Also, the jitter attenuator can be dis-

abled (in effect, removed) by setting the DJA bit in the

LICR. In order for the jitter attenuator to operate prop-

erly, a 1.544 MHz clock (

±

50 ppm) must be applied at the

MCLK pin or a crystal with similar characteristics must

be applied across the MCLK and XTALD pins. If a crys-

tal is applied across the MCLK and XTALD pins, then

the maximum effective series resistance (ESR) should

be 40 Ohms and capacitors should be placed from each

leg of the crystal to the local ground plane as shown in

Figure 14–1. Onboard circuitry adjusts either the recov-

ered clock from the clock/data recovery block or the

clock applied at the TCLKI pin to create a smooth jitter

free clock which is used to clock data out of the jitter

attenuator FIFO. It is acceptable to provide a gapped/

bursty clock at the TCLKI pin if the jitter attenuator is

placed on the transmit side. If the incoming jitter

exceeds either 120 UIpp (buffer depth is 128 bits) or 28

UIpp (buffer depth is 32 bits), then the DS2152 will

divide the internal nominal 24.704 MHz clock by either

15 or 17 instead of the normal 16 to keep the buffer from

overflowing. When the device divides by either 15 or 17,

it also sets the Jitter Attenuator Limit Trip (JALT) bit in

the Receive Information Register (RIR3.5).