Rainbow Electronics DS2152 User Manual

Page 29

DS2152

031897 29/79

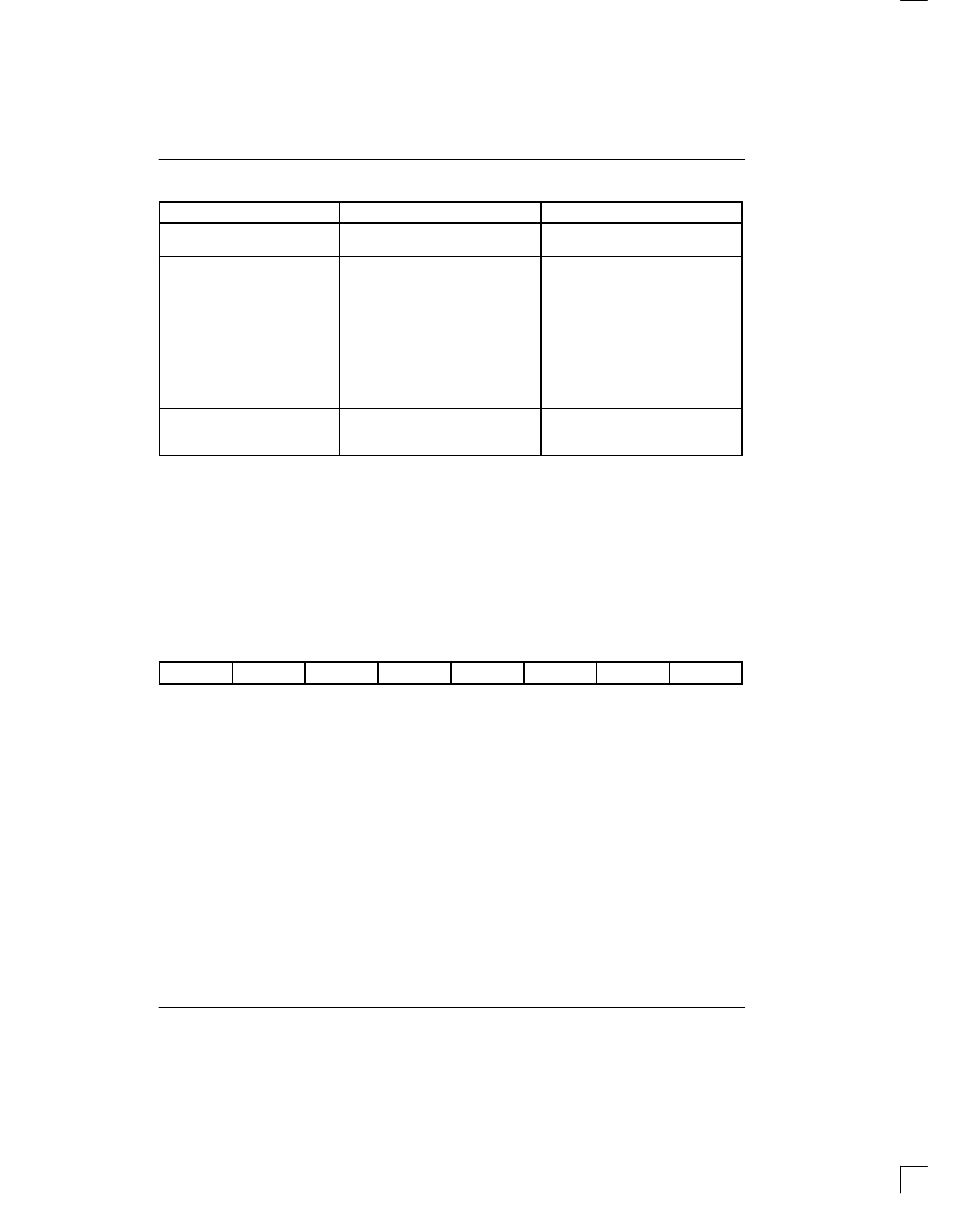

ALARM CRITERIA Table 4–2

ALARM

SET CRITERIA

CLEAR CRITERIA

Blue Alarm (AIS)

(see note 1 below)

when over a 3 ms window,

5 or less zeros are received

when over a 3 ms window,

6 or more zeros are received

Yellow Alarm (RAI)

1. D4 bit 2 mode(RCR2.2=0)

2. D4 12th F–bit mode

(RCR2.2=1; this mode is also

referred to as the “Japanese

Yellow Alarm”)

3. ESF mode

when bit 2 of 256 consecutive chan-

nels is set to zero for at least 254

occurrences

when the 12th framing bit is set to

one for two consecutive occur-

rences

when 16 consecutive patterns of

00FF appear in the FDL

when bit 2 of 256 consecutive chan-

nels is set to zero for less than 254

occurrences

when the 12th framing bit is set to

zero for two consecutive occur-

rences

when 14 or less patterns of 00FF

hex out of 16 possible appear in the

FDL

Red Alarm (LRCL)

(this alarm is also referred to as

Loss Of Signal)

when 192 consecutive zeros

are received

when 14 or more ones out of 112

possible bit positions are received

starting with the first one received

NOTES:

1. The definition of Blue Alarm (or Alarm Indication Sig-

nal) is an unframed all ones signal. Blue alarm

detectors should be able to operate properly in the

presence of a 10–3 error rate and they should not

falsely trigger on a framed all ones signal. The blue

alarm criteria in the DS2152 has been set to achieve

this performance. It is recommended that the RBL

bit be qualified with the RLOS bit.

2. ANSI specifications use a different nomenclature

than the DS2152 does; the following terms are

equivalent:

RBL = AIS

LRCL = LOS

RLOS = LOF

RYEL = RAI

SR2: STATUS REGISTER 2 (Address=21 Hex)

(MSB)

(LSB)

RMF

TMF

SEC

RFDL

TFDL

RMTCH

RAF

RSC

SYMBOL

POSITION

NAME AND DESCRIPTION

RMF

SR2.7

Receive Multiframe. Set on receive multiframe boundaries.

TMF

SR2.6

Transmit Multiframe. Set on transmit multiframe boundaries.

SEC

SR2.5

One Second Timer. Set on increments of one second based on RCLK; will

be set in increments of 999 ms, 999 ms, and 1002 ms every 3 seconds.

RFDL

SR2.4

Receive FDL Buffer Full. Set when the receive FDL buffer (RFDL) fills to

capacity (8 bits).

TFDL

SR2.3

Transmit FDL Buffer Empty. Set when the transmit FDL buffer (TFDL)

empties.

RMTCH

SR2.2

Receive FDL Match Occurrence. Set when the RFDL matches either

RFDLM1 or RFDLM2.

RAF

SR2.1

Receive FDL Abort. Set when eight consecutive one’s are received in the

FDL.

RSC

SR2.0

Receive Signaling Change. Set when the DS2152 detects a change of

state in any of the robbed–bit signaling bits.