Rainbow Electronics DS2152 User Manual

Page 56

DS2152

031897 56/79

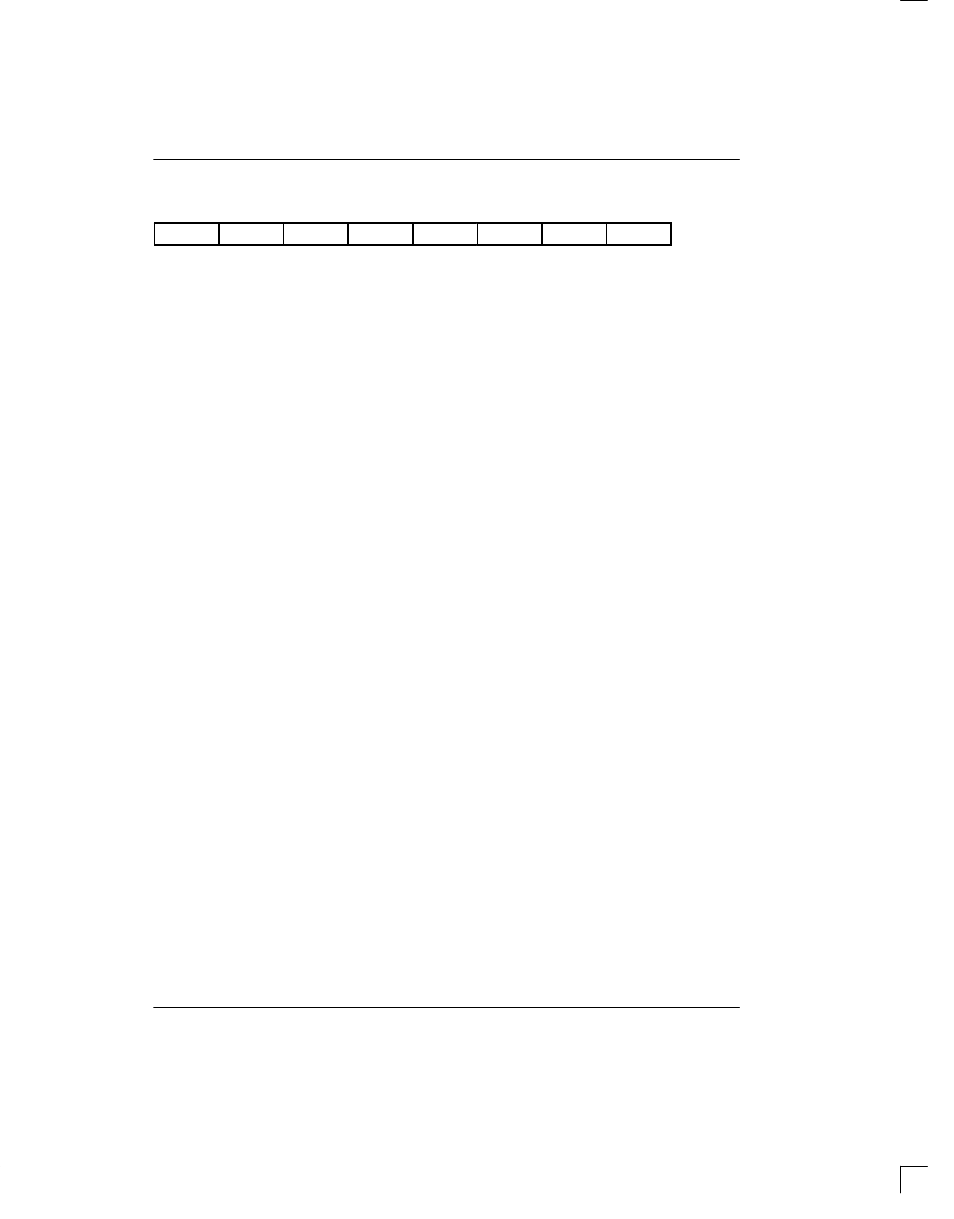

LICR: LINE INTERFACE CONTROL REGISTER (Address=7C Hex)

(MSB)

(LSB)

L2

L1

L0

EGL

JAS

JABDS

DJA

TPD

SYMBOL

POSITION

NAME AND DESCRIPTION

L2

LICR.7

Line Build Out Select Bit 2. Sets the transmitter build out; see the

Table 14–2

L1

LICR.6

Line Build Out Select Bit 1. Sets the transmitter build out; see the

Table 14–2

L0

LICR.5

Line Build Out Select Bit 0. Sets the transmitter build out; see the

Table 14–2

EGL

LICR.4

Receive Equalizer Gain Limit.

0 = –36 dB

1 = –30 dB

JAS

LICR.3

Jitter Attenuator Select.

0 = place the jitter attenuator on the receive side

1 = place the jitter attenuator on the transmit side

JABDS

LICR.2

Jitter Attenuator Buffer Depth Select

0 = 128 bits

1 = 32 bits (use for delay sensitive applications)

DJA

LICR.1

Disable Jitter Attenuator.

0 = jitter attenuator enabled

1 = jitter attenuator disabled

TPD

LICR.0

Transmit Power Down.

0 = normal transmitter operation

1 = powers down the transmitter and 3–states the TTIP and TRING pins

14.1 RECEIVE CLOCK AND DATA

RECOVERY

The DS2152 contains a digital clock recovery system.

See the DS2152 Block Diagram in Section 1 and

Figure 14–1 for more details. The DS2152 couples to

the receive T1 twisted pair via a 1:1 transformer. See

Table 14–3 for transformer details. The 1.544 MHz clock

attached at the MCLK pin is internally multiplied by 16

via an internal PLL and fed to the clock recovery system.

The clock recovery system uses the clock from the PLL

circuit to form a 16 times oversampler which is used to

recover the clock and data. This oversampling tech-

nique offers outstanding jitter tolerance (see Figure

14–2).

Normally, the clock that is output at the RCLKO pin is the

recovered clock from the T1 AMI/B8ZS waveform pres-

ented at the RTIP and RRING inputs. When no AMI sig-

nal is present at RTIP and RRING, a Receive Carrier

Loss (LRCL) condition will occur and the RCLKO will be

sourced from the clock applied at the MCLK pin. If the

jitter attenuator is either placed in the transmit path or is

disabled, the RCLKO output can exhibit slightly shorter

high cycles of the clock. This is due to the highly over-

sampled digital clock recovery circuitry. If the jitter

attenuator is placed in the receive path (as is the case in

most applications), the jitter attenuator restores the

RCLK to being close to 50% duty cycle. Please see the

Receive AC Timing Characteristics in Section 16 for

more details.

14.2 TRANSMIT WAVESHAPING AND LINE

DRIVING

The DS2152 uses a set of laser–trimmed delay lines

along with a precision Digital–to–Analog Converter

(DAC) to create the waveforms that are transmitted onto

the T1 line. The waveforms created by the DS2152

meet the latest ANSI, AT&T, and ITU specifications.

See Figure 14–3. The user will select which waveform

is to be generated by properly programming the

L2/L1/L0 bits in the Line Interface Control Register

(LICR). The DS2152 can set set up in a number of vari-

ous configurations depending on the application. See

Table 14–2 and Figure 14–1.

LICR