Rainbow Electronics DS2152 User Manual

Page 37

DS2152

031897 37/79

of a change in signaling by setting the IMR2.0 bit. Once

a signaling change has been detected, the user has at

least 2.75 ms to read the data out of the RS1 to RS12

registers before the data will be lost.

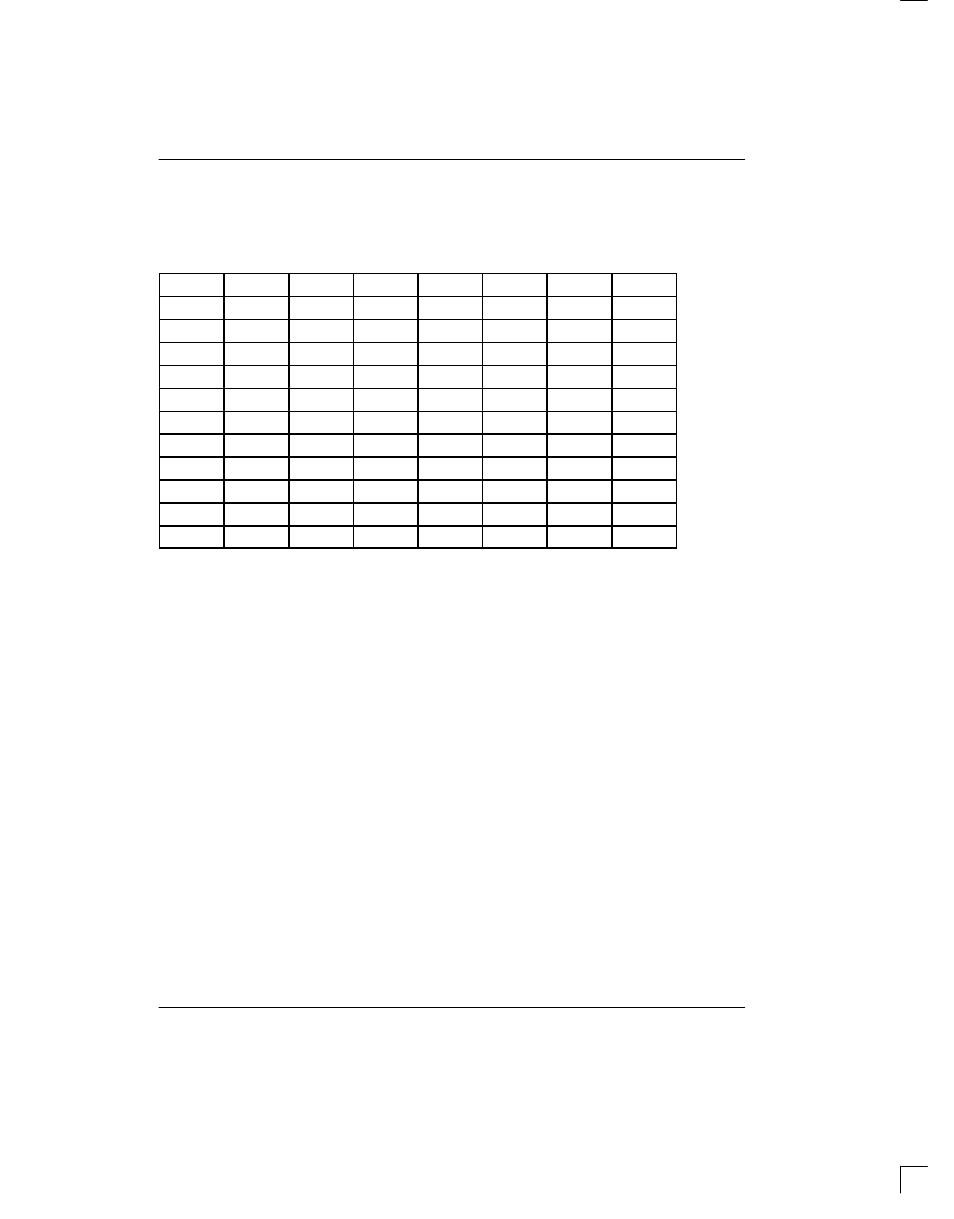

TS1 TO TS12: TRANSMIT SIGNALING REGISTERS (Address=70 to 7B Hex)

(MSB)

(LSB)

A(8)

A(7)

A(6)

A(5)

A(4)

A(3)

A(2)

A(1)

A(16)

A(15)

A(14)

A(13)

A(12)

A(11)

A(10)

A(9)

A(24)

A(23)

A(22)

A(21)

A(20)

A(19)

A(18)

A(17)

B(8)

B(7)

B(6)

B(5)

B(4)

B(3)

B(2)

B(1)

B(16)

B(15)

B(14)

B(13)

B(12)

B(11)

B(10)

B(9)

B(24)

B(23)

B(22)

B(21)

B(20)

B(19)

B(18)

B(17)

A/C(8)

A/C(7)

A/C(6)

A/C(5)

A/C(4)

A/C(3)

A/C(2)

A/C(1)

A/C(16)

A/C(15)

A/C(14)

A/C(13)

A/C(12)

A/C(11)

A/C(10)

A/C(9)

A/C(24)

A/C(23)

A/C(22)

A/C(21)

A/C(20)

A/C(19)

A/C(18)

A/C(17)

B/D(8)

B/D(7)

B/D(6)

B/D(5)

B/D(4)

B/D(3)

B/D(2)

B/D(1)

B/D(16)

B/D(15)

B/D(14)

B/D(13)

B/D(12)

B/D(11)

B/D(10)

B/D(9)

B/D(24)

B/D(23)

B/D(22)

B/D(21)

B/D(20)

B/D(19)

B/D(18)

B/D(17)

SYMBOL

POSITION

NAME AND DESCRIPTION

D(24)

TS12.7

Signaling Bit A in Channel 24

A(1)

TS1.0

Signaling Bit D in Channel 1

Each Transmit Signaling Register (TS1 to TS12) con-

tains the Robbed Bit signaling for eight DS0 channels

that will be inserted into the outgoing stream if enabled

to do so via TCR1.4. In the ESF framing mode, there

can be up to four signaling bits per channel (A, B, C, and

D). On multiframe boundaries, the DS2152 will load the

values present in the Transmit Signaling Register into

an outgoing signaling shift register that is internal to the

device. The user can utilize the Transmit Multiframe

Interrupt in Status Register 2 (SR2.6) to know when to

update the signaling bits. In the ESF framing mode, the

interrupt will come every 3 ms and the user has a full

3ms to update the TSRs. In the D4 framing mode, there

are only two framing bits per channel (A and B). How-

ever in the D4 framing mode, the DS2152 uses the C

and D bit positions as the A and B bit positions for the

next multiframe. The DS2152 will load the values in the

TSRs into the outgoing shift register every other D4 mul-

tiframe.

7.2

HARDWARE BASED SIGNALING

7.2.1

Receive Side

In the receive side of the hardware based signaling,

there are two operating modes for the signaling buffer;

signaling extraction and signaling re–insertion. Signal-

ing extraction involves pulling the signaling bits from the

receive data stream and buffering them over a four mul-

tiframe buffer and outputing them in a serial PCM fash-

ion on a channel–by–channel basis at the RSIG output.

This mode is always enabled. In this mode, the receive

elastic store may be enabled or disabled. If the receive

elastic store is enabled, then the backplane clock

(RSYSCLK) can be either 1.544 MHz or

2.048 MHz. In the ESF framing mode, the ABCD signal-

ing bits are output on RSIG in the lower nibble of each

channel. The RSIG data is updated once a multiframe

(3 ms) unless a freeze is in effect. In the D4 framing

mode, the AB signaling bits are output twice on RSIG in

TS1 (70)

TS2 (71)

TS3 (72)

TS4 (73)

TS5 (74)

TS6 (75)

TS7 (76)

TS8 (77)

TS9 (78)

TS10 (79)

TS11 (7A)

TS12 (7B)