Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 57

Control Register File Extensions

2-31

CPU Data Paths and Control

SPRU733

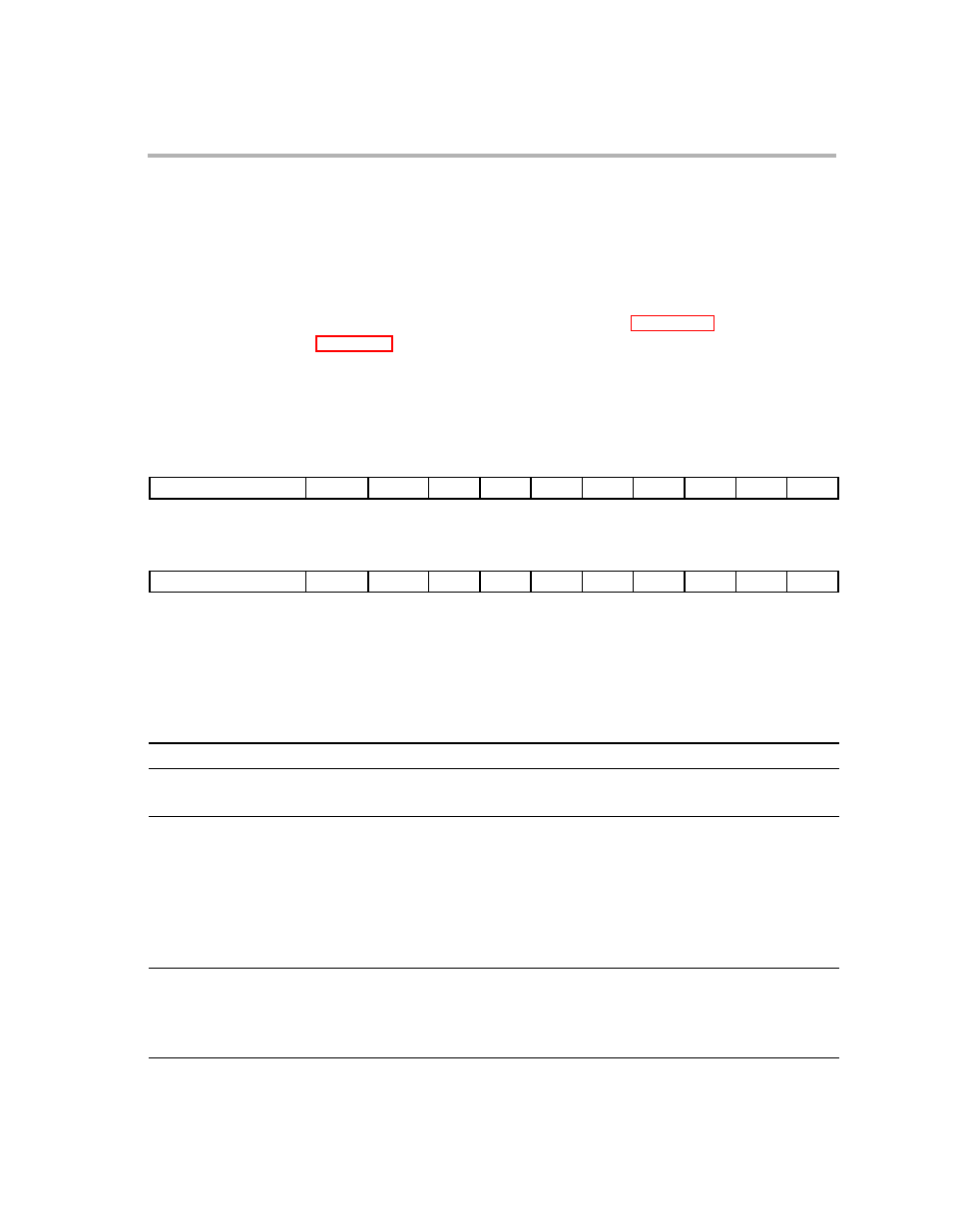

2.8.3 Floating-Point Multiplier Configuration Register (FMCR)

The floating-point multiplier configuration register (FMCR) contains fields that

specify underflow or overflow, the rounding mode, NaNs, denormalized

numbers, and inexact results for instructions that use the .M functional units.

FMCR has a set of fields specific to each of the .M units: .M2 uses bits 31−16

and .M1 uses bits 15−0. FMCR is shown in Figure 2−16 and described in

Table 2−16.

Figure 2−16. Floating-Point Multiplier Configuration Register (FMCR)

31

27 26

25

24

23

22

21

20

19

18

17

16

Reserved

RMODE

UNDER

INEX

OVER

INFO

INVAL

DEN2

DEN1

NAN2

NAN1

R-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

15

11 10

9

8

7

6

5

4

3

2

1

0

Reserved

RMODE

UNDER

INEX

OVER

INFO

INVAL

DEN2

DEN1

NAN2

NAN1

R-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

Legend: R = Readable by the MVC instruction; W = Writeable by the MVC instruction; -n = value after reset

Table 2−16. Floating-Point Multiplier Configuration Register (FMCR)

Field Descriptions

Bit

Field

Value Description

31−27 Reserved

0

Reserved. The reserved bit location is always read as 0. A value written to this

field has no effect.

26−25 RMODE

0−3h

Rounding mode select for .M2.

0

Round toward nearest representable floating-point number

1h

Round toward 0 (truncate)

2h

Round toward infinity (round up)

3h

Round toward negative infinity (round down)

24

UNDER

Result underflow status for .M2.

0

Result does not underflow.

1

Result underflows.