Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 370

Functional Unit Constraints

Pipeline

4-38

SPRU733

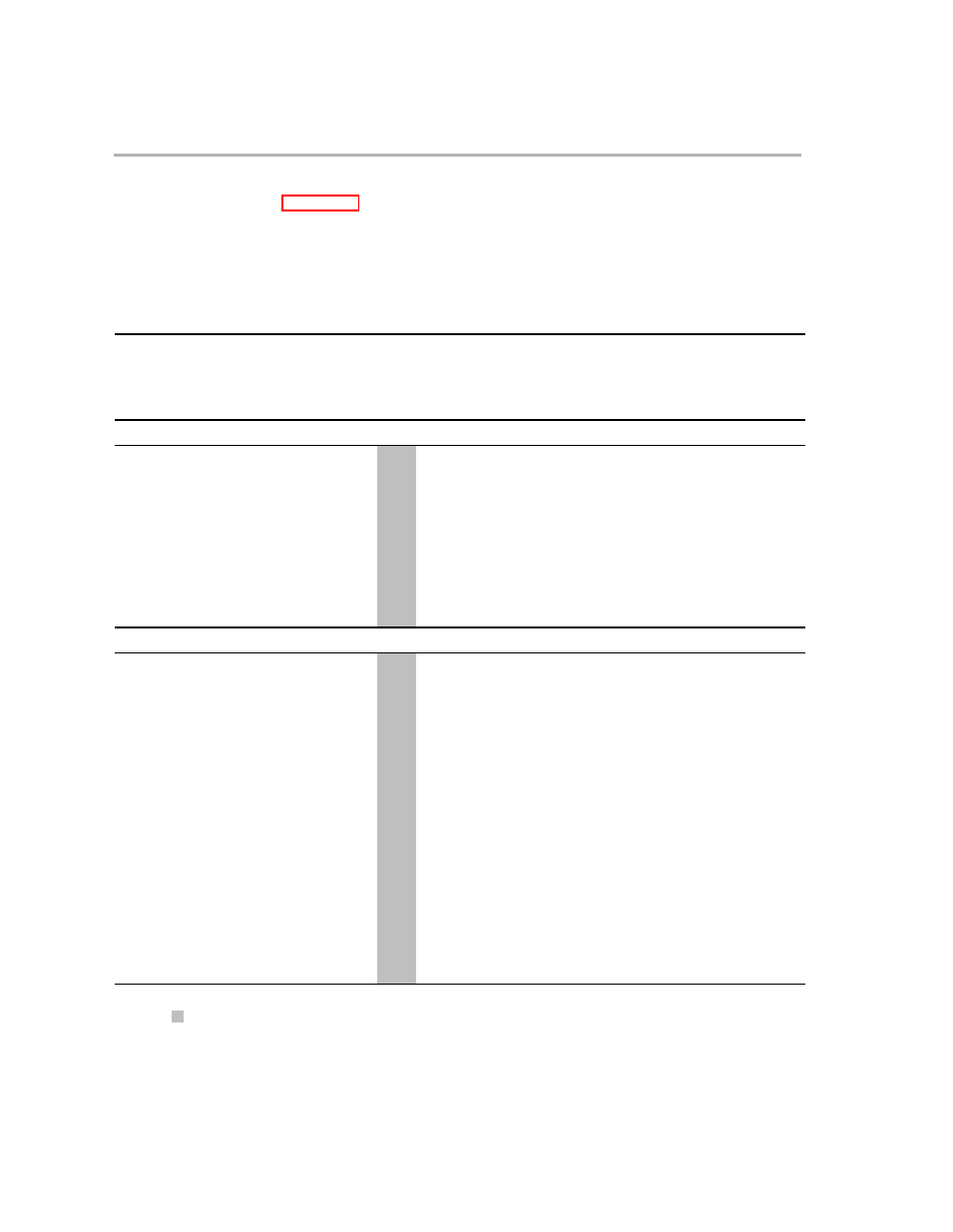

Table 4−22 shows the instruction constraints for ADDDP/SUBDP instructions

executing on the .S unit.

Table 4−22. ADDDP/SUBDP .S-Unit Instruction Constraints

Instruction Execution

Cycle

1

2

3

4

5

6

7

ADDDP/SUBDP

R

R

W

W

Instruction Type

Subsequent Same-Unit Instruction Executable

Single-cycle

Xr

n

n

n

Xw

Xw

2-cycle DP

Xr

n

n

Xw

Xw

Xw

DP compare

Xr

n

n

Xw

Xw

n

ADDDP/SUBDP

Xr

n

n

n

n

n

ADDSP/SUBSP

Xr

Xw

Xw

n

n

n

Branch

Xr

n

n

n

n

n

Instruction Type

Same Side, Different Unit, Both Using Cross Path Executable

Single-cycle

Xr

n

n

n

n

n

DP compare

Xr

n

n

n

n

n

2-cycle DP

Xr

n

n

n

n

n

4-cycle

Xr

n

n

n

n

n

Load

n

n

n

n

n

n

Store

n

n

n

n

n

n

Branch

Xr

n

n

n

n

n

16 × 16 multiply

Xr

n

n

n

n

n

MPYI

Xr

n

n

n

n

n

MPYID

Xr

n

n

n

n

n

MPYDP

Xr

n

n

n

n

n

Legend:

= E1 phase of the single-cycle instruction; R = Sources read for the instruction; W = Destinations written for the

instruction;

n

= Next instruction can enter E1 during cycle; Xr = Next instruction cannot enter E1 during cycle-read/

decode constraint; Xw = Next instruction cannot enter E1 during cycle−write constraint