Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 271

Set a Bit Field

SET

3-211

Instruction Set

SPRU733

Description

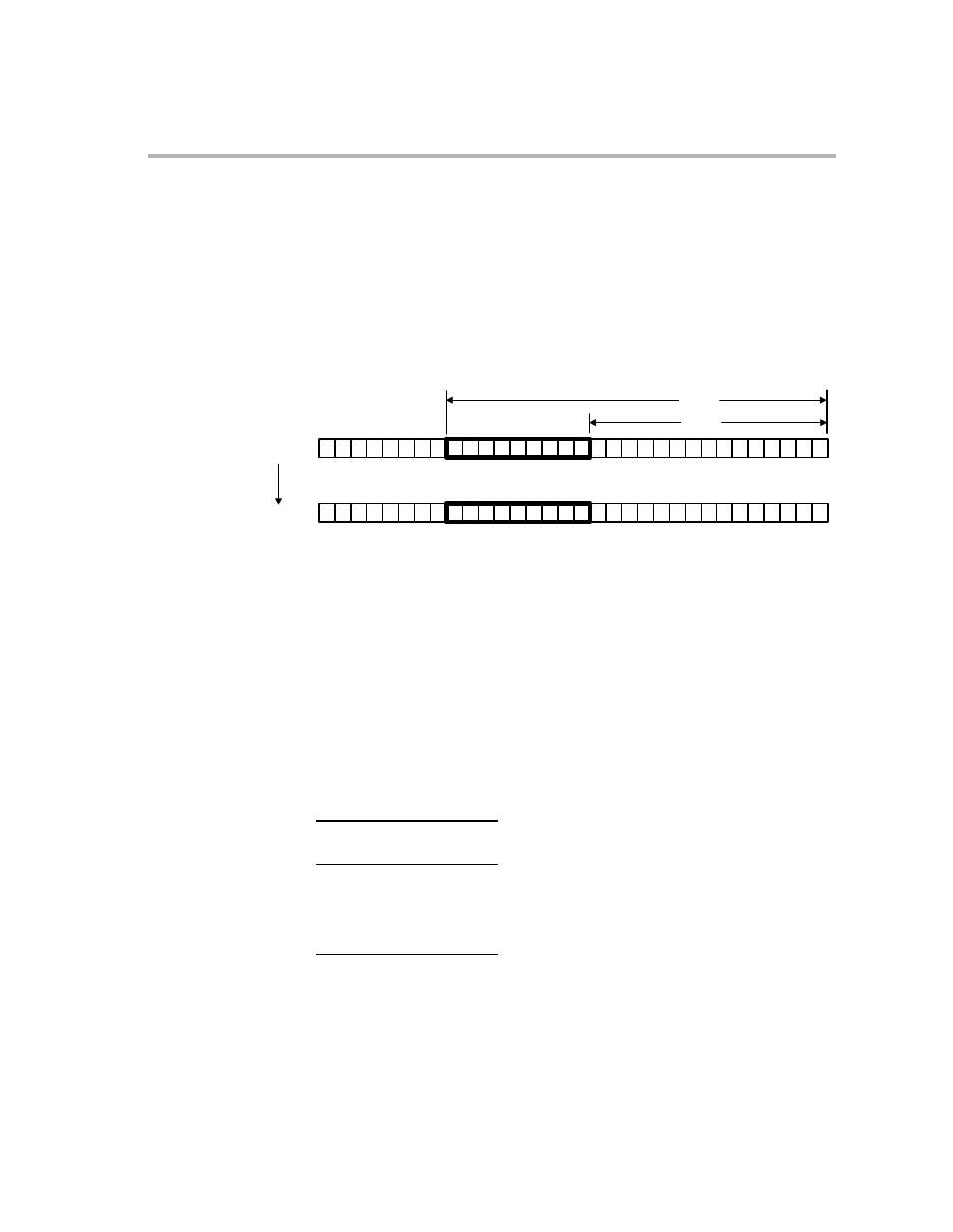

The field in src2, specified by csta and cstb, is set to all 1s. The csta and cstb

operands may be specified as constants or in the ten LSBs of the src1 register,

with cstb being bits 0−4 and csta bits 5−9. csta signifies the bit location of the

LSB of the field and cstb signifies the bit location of the MSB of the field. In other

words, csta and cstb represent the beginning and ending bits, respectively, of

the field to be set to all 1s. The LSB location of src2 is 0 and the MSB location

of src2 is 31. In the example below, csta is 15 and cstb is 23. Only the ten LSBs

are valid for the register version of the instruction. If any of the 22 MSBs are

non-zero, the result is invalid.

src2

dst

0

x x x x x x x x

x x x x x x x x x x x x x x x

1

1

1 1

1

0

0

0

x x x x x x x x

x x x x x x x x x x x x x x x

1 1

1

1 1

1

1

1

1

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8

7 6

5 4

3 2 1 0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8

7 6

5 4

3 2 1 0

csta

cstb

Execution

If the constant form is used:

if (cond)

src2 SET csta, cstb

→

dst

else nop

If the register form is used:

if (cond)

src2 SET src1

9..5

,

src1

4..0

→

dst

else nop

Pipeline

Stage

E1

Read

src1, src2

Written

dst

Unit in use

.S

Instruction Type

Single-cycle

Delay Slots

0

See Also

CLR

Pipeline