13 mpydp instruction – Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 363

Pipeline Execution of Instruction Types

4-31

Pipeline

SPRU733

4.2.13 MPYDP Instruction

The MPYDP instruction uses the E1 through E10 phases of the pipeline to

complete its operations (see Table 4−15). The lower 32 bits of src1 are read

on E1 and E2, and the upper 32 bits of src1 are read on E3 and E4. The lower

32 bits of src2 are read on E1 and E3, and the upper 32 bits of src2 are read

on E2 and E4. The lower 32 bits of the result are written on E9, and the upper

32 bits of the result are written on E10. The MPYDP instruction is executed on

the .M unit. The functional unit latency for the MPYDP instruction is 4. The

status is written to the FMCR on E9. Figure 4−25 shows the fetch, decode, and

execute phases of the pipeline that the MPYDP instruction uses.

Table 4−15. MPYDP Instruction Execution

Pipeline

Stage

E1

E2

E3

E4

E5

E6

E7

E8

E9

E10

Read

src1_l

src2_l

src1_l

src2_h

src1_h

src2_l

src1_h

src2_h

Written

dst_l dst_h

Unit in use

.M

.M

.M

.M

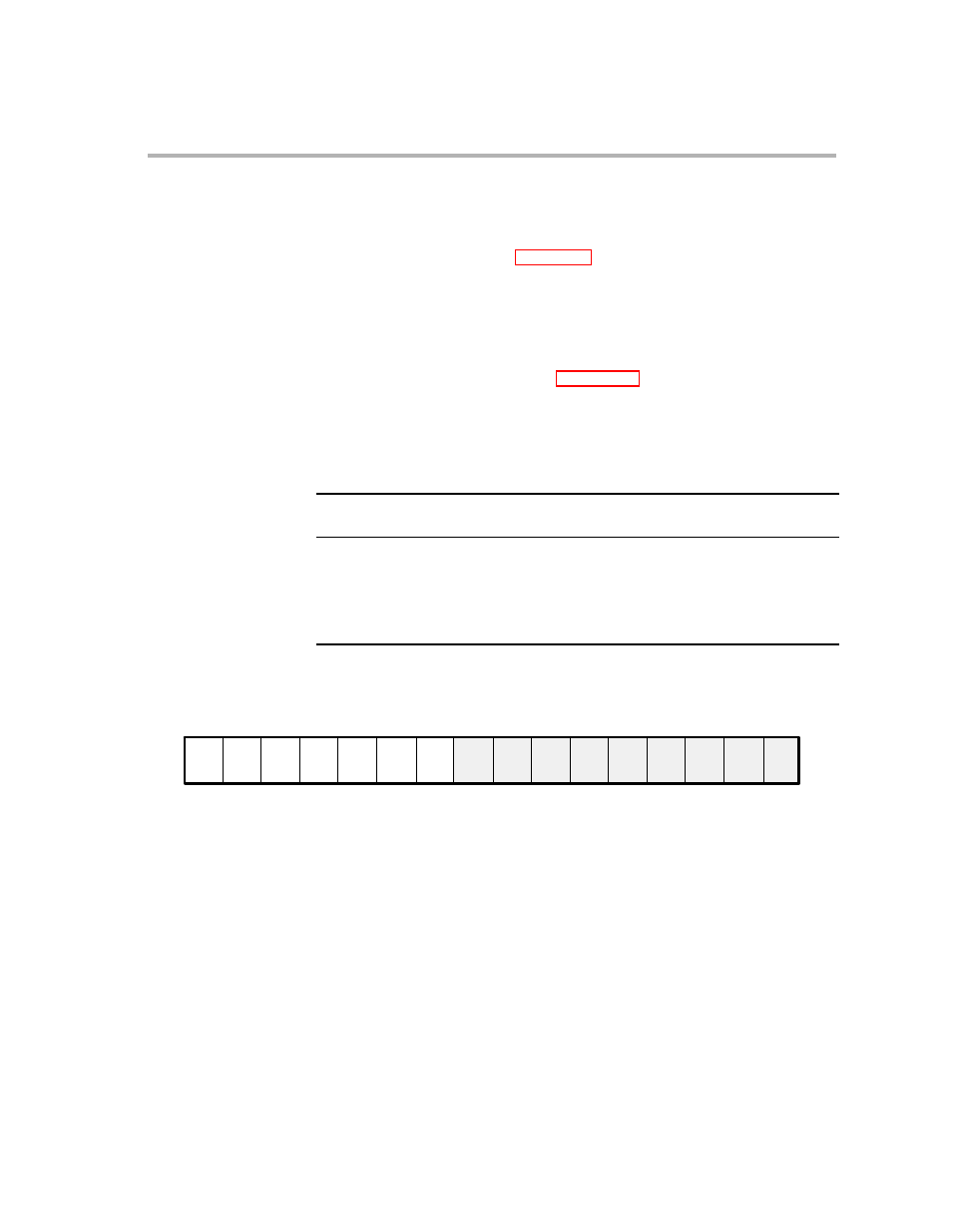

Figure 4−25. MPYDP Instruction Phases

PG

PS

PW

PR

DP

DC

E1

E2

E3

E4

E5

E6

E7

E8

E9 E10

9 delay slots