Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 258

RCPDP

Double-Precision Floating-Point Reciprocal Approximation

3-198

Instruction Set

SPRU733

Note:

1) If src2 is SNaN, NaN_out is placed in dst and the INVAL and NAN2 bits

are set.

2) If src2 is QNaN, NaN_out is placed in dst and the NAN2 bit is set.

3) If src2 is a signed denormalized number, signed infinity is placed in dst

and the DIV0, INFO, OVER, INEX, and DEN2 bits are set.

4) If src2 is signed 0, signed infinity is placed in dst and the DIV0 and INFO

bits are set.

5) If src2 is signed infinity, signed 0 is placed in dst.

6) If the result underflows, signed 0 is placed in dst and the INEX and

UNDER bits are set. Underflow occurs when 2

1022

t src2 t infinity.

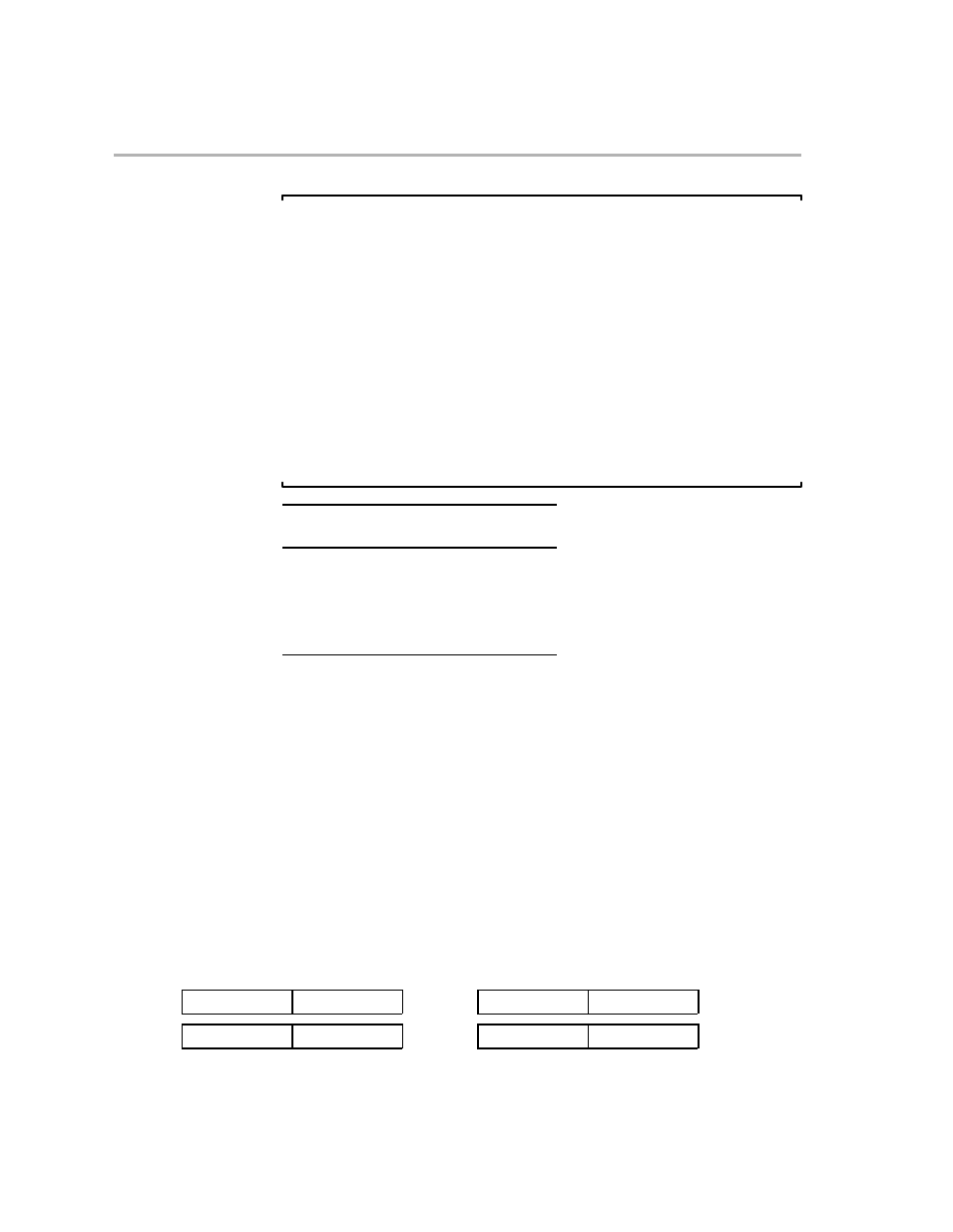

Pipeline

Stage

E1

E2

Read

src2_l

src2_h

Written

dst_l

dst_h

Unit in use

.S

If dst is used as the source for the ADDDP, CMPEQDP, CMPLTDP,

CMPGTDP, MPYDP, or SUBDP instruction, the number of delay slots can be

reduced by one, because these instructions read the lower word of the DP

source one cycle before the upper word of the DP source.

Instruction Type

2-cycle DP

Delay Slots

1

Functional Unit

Latency

1

See Also

RCPSP, RSQRDP

Example

RCPDP .S1

A1:A0,A3:A2

Before instruction

2 cycles after instruction

A1:A0 4010 0000h

0000 0000h

A1:A0 4010 0000h

0000 0000h

4.00

A3:A2 xxxx xxxxh

xxxx xxxxh

A3:A2 3FD0 0000h

0000 0000h

0.25

Pipeline