Shru, Logical shift right shru – Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 277

Logical Shift Right

SHRU

3-217

Instruction Set

SPRU733

Logical Shift Right

SHRU

Syntax

SHRU (.unit) src2, src1, dst

.unit = .S1 or .S2

Compatibility

C62x, C64x, C67x, and C67x+ CPU

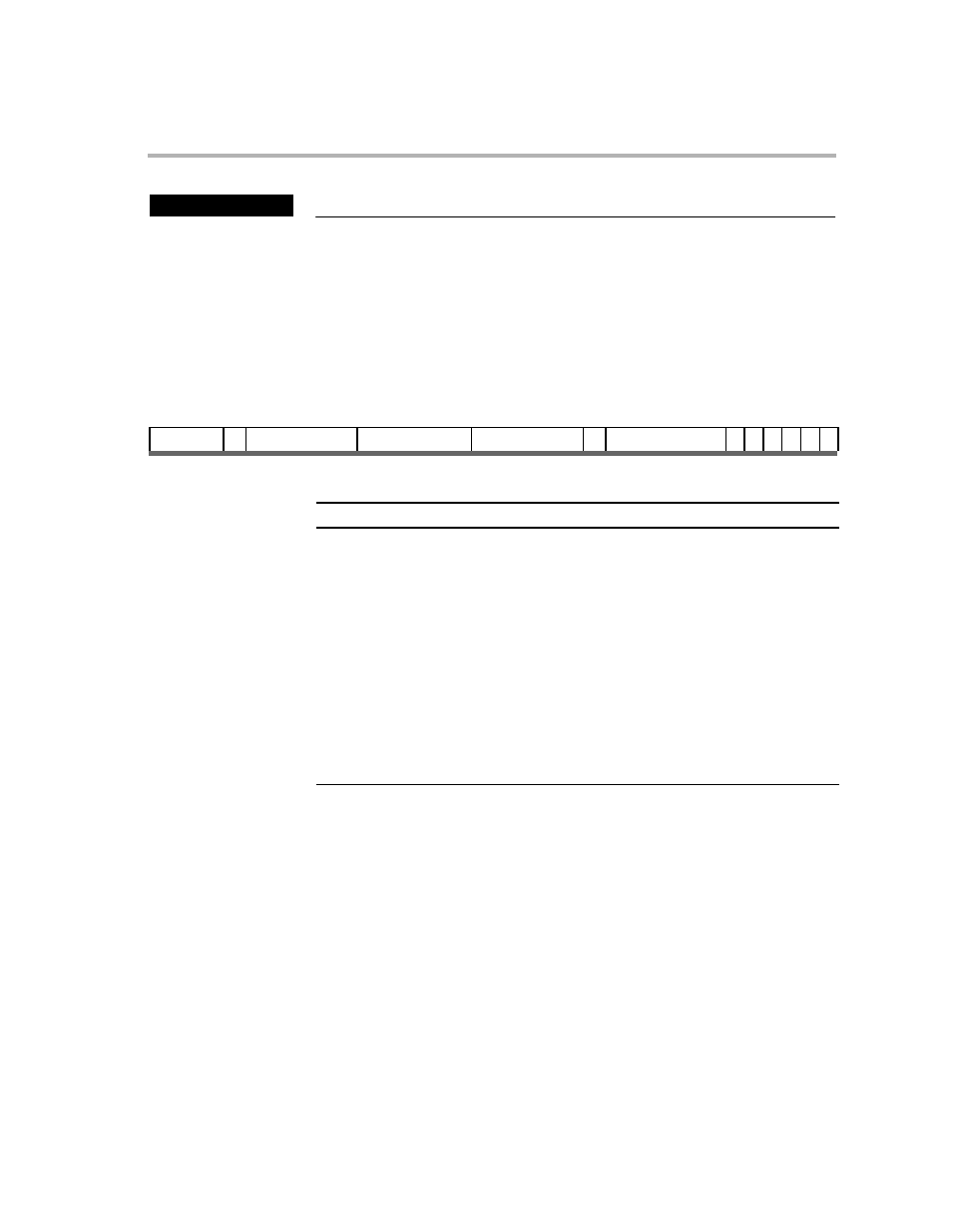

Opcode

31

29

28

27

23

22

18

17

13

12

11

6

5

4

3

2

1

0

creg

z

dst

src2

src1

x

op

1 0 0 0 s p

3

1

5

5

5

1

6

1

1

Opcode map field used...

For operand type...

Unit

Opfield

src2

src1

dst

xuint

uint

uint

.S1, .S2

10 0111

src2

src1

dst

ulong

uint

ulong

.S1, .S2

10 0101

src2

src1

dst

xuint

ucst5

uint

.S1, .S2

10 0110

src2

src1

dst

ulong

ucst5

ulong

.S1, .S2

10 0100

Description

The src2 operand is shifted to the right by the src1 operand. The

zero-extended result is placed in dst. When a register is used, the six LSBs

specify the shift amount and valid values are 0–40. When an immediate value

is used, valid shift amounts are 0–31.

If 39

<

src1

<

64, src2 is shifted to the right by 40. Only the six LSBs of src1 are

used by the shifter, so any bits set above bit 5 do not affect execution.

Execution

if (cond)

src2

>>

z src1

→

dst

else nop