15 mpysp2dp instruction, 3 functional unit constraints – Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 365

Functional Unit Constraints

4-33

Pipeline

SPRU733

4.2.15 MPYSP2DP Instruction

The MPYSP2DP instruction uses the E1 through E5 phases of the pipeline to

complete its operations (see Table 4−17). src1 and src2 are read on E1. The

lower 32 bits of the result are written on E4, and the upper 32 bits of the result

are written on E5. The MPYSP2DP instruction is executed on the .M unit. The

functional unit latency for the MPYSP2DP instruction is 2. Figure 4−27 shows

the fetch, decode, and execute phases of the pipeline that the MPYSP2DP

instruction uses.

Table 4−17. MPYSP2DP Instruction Execution

Pipeline Stage

E1

E2

E3

E4

E5

Read

src1

src2

Written

dst_l

dst_h

Unit in use

.M

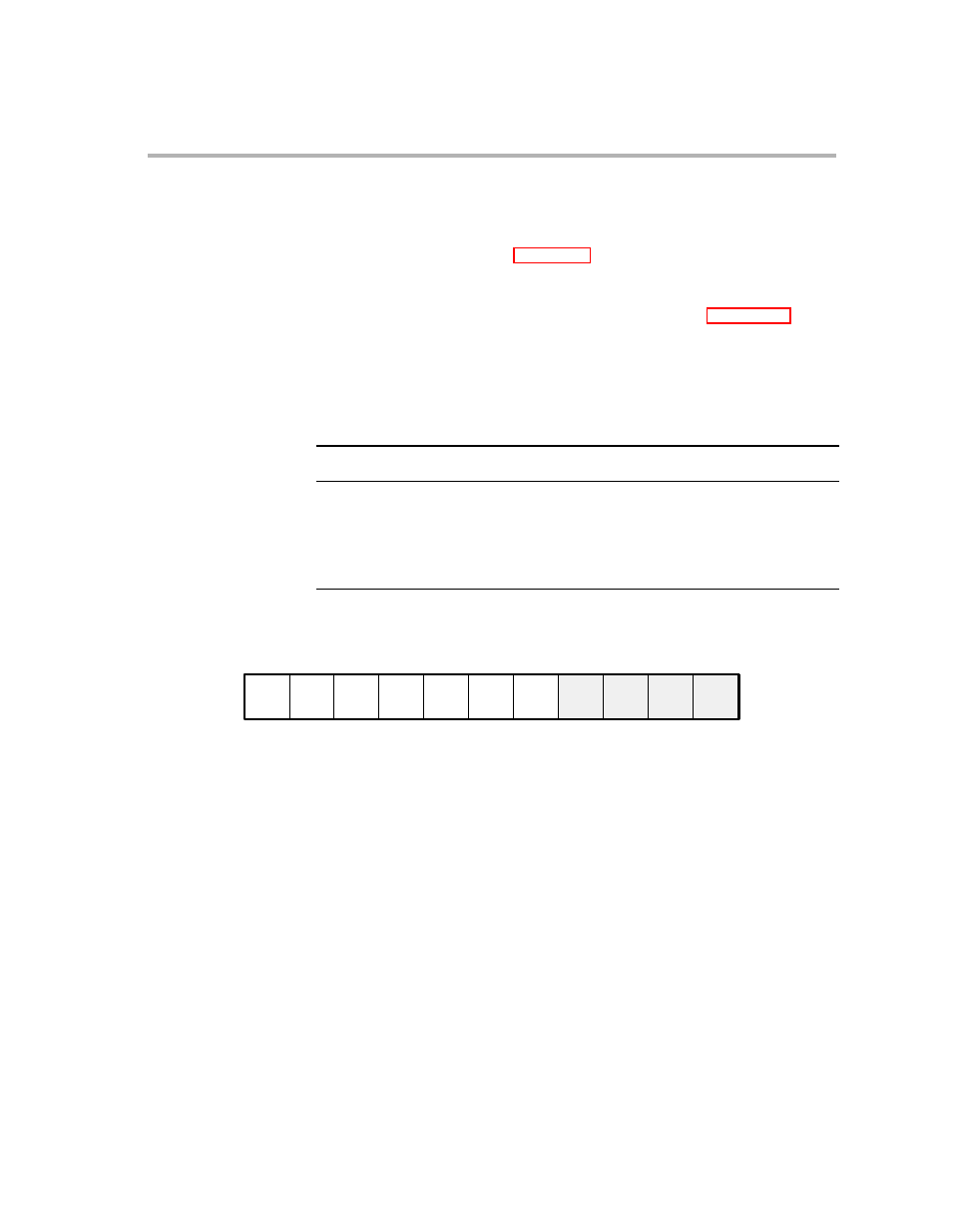

Figure 4−27. MPYSP2DP Instruction Phases

PG

PS

PW

PR

DP

DC

E1

E2

E3

E4

E5

4 delay slots

4.3 Functional Unit Constraints

If you want to optimize your instruction pipeline, consider the instructions that

are executed on each unit. Sources and destinations are read and written

differently for each instruction. If you analyze these differences, you can make

further optimization improvements by considering what happens during the

execution phases of instructions that use the same functional unit in each

execution packet.

The following sections provide information about what happens during each

execute phase of the instructions within a category for each of the functional

units.

Pipeline Execution of Instruction Types / Functional Unit Constraints