Sshl, Shift left with saturation sshl – Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 292

SSHL

Shift Left With Saturation

3-232

Instruction Set

SPRU733

Shift Left With Saturation

SSHL

Syntax

SSHL (.unit) src2, src1, dst

.unit = .S1 or .S2

Compatibility

C62x, C64x, C67x, and C67x+ CPU

Opcode

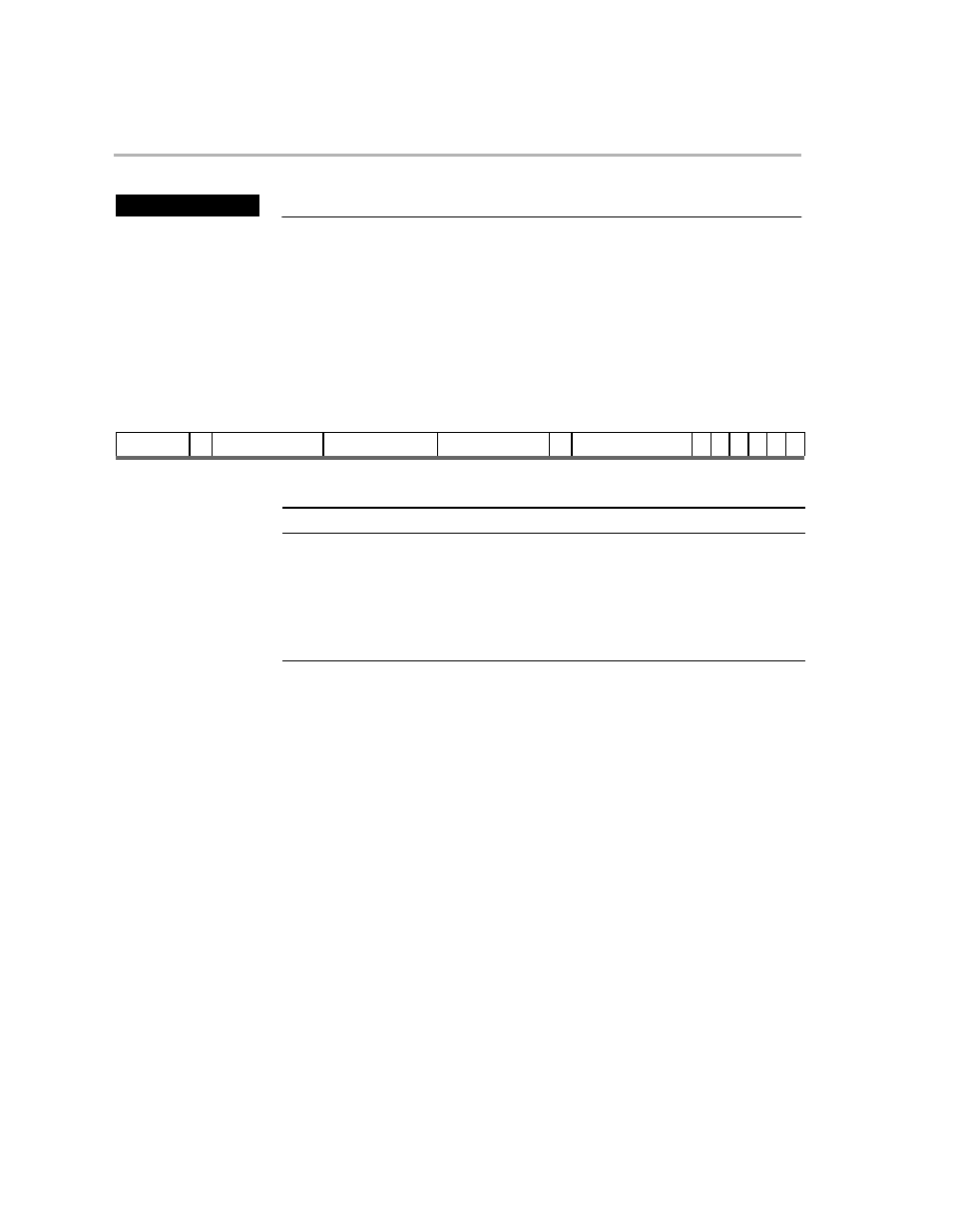

31

29

28

27

23

22

18

17

13

12

11

6

5

4

3

2

1

0

creg

z

dst

src2

src1

x

op

1 0 0 0 s p

3

1

5

5

5

1

6

1

1

Opcode map field used...

For operand type...

Unit

Opfield

src2

src1

dst

xsint

uint

sint

.S1, .S2

10 0011

src2

src1

dst

xsint

ucst5

sint

.S1, .S2

10 0010

Description

The src2 operand is shifted to the left by the src1 operand. The result is placed

in dst. When a register is used to specify the shift, the five least significant bits

specify the shift amount. Valid values are 0 through 31, and the result of the

shift is invalid if the shift amount is greater than 31. The result of the shift is

saturated to 32 bits. If a saturate occurs, the SAT bit in CSR is set one cycle

after dst is written.

Execution

if (cond)

{

if ( bit(31) through bit(31−src1) of src2 are all 1s or all 0s)

dst = src2 << src1;

else if (src2 > 0)

saturate dst to 7FFF FFFFh;

else if (src2 < 0)

saturate dst to 8000 0000h;

}

else nop