3 memory considerations – Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 392

Performance Considerations

Pipeline

4-60

SPRU733

4.4.3 Memory Considerations

The C67x DSP has a memory configuration with program memory in one

physical space and data memory in another physical space. Data loads and

program fetches have the same operation in the pipeline, they just use differ-

ent phases to complete their operations. With both data loads and program

fetches, memory accesses are broken into multiple phases. This enables the

C67x DSP to access memory at a high speed. These phases are shown in

Figure 4−31.

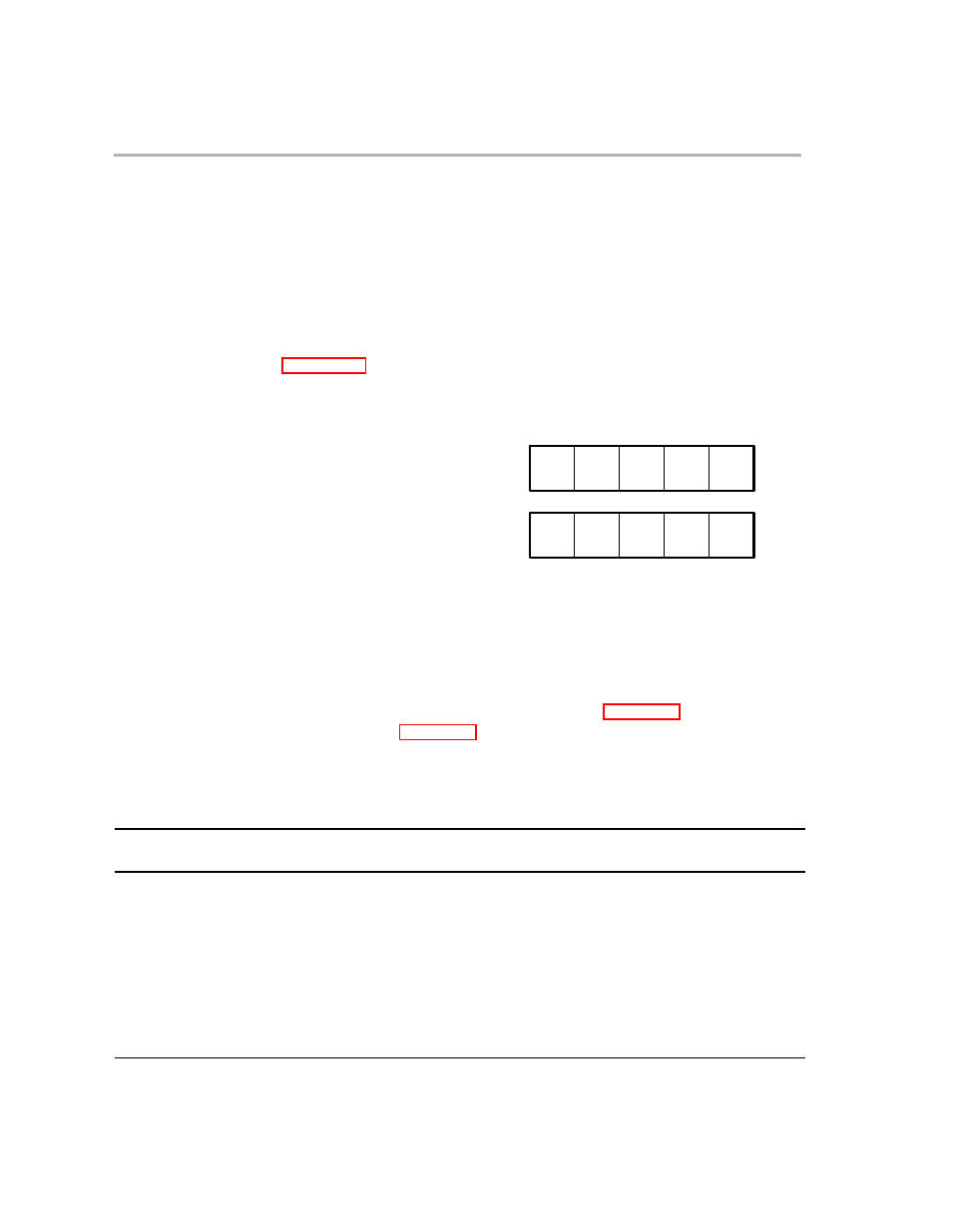

Figure 4−31. Pipeline Phases Used During Memory Accesses

Program memory accesses use these pipeline phases

Data load accesses use these pipeline phases

PG

PS

PW

PR

DP

E1

E2

E3

E4

E5

To understand the memory accesses, compare data loads and instruction

fetches/dispatches. The comparison is valid because data loads and program

fetches operate on internal memories of the same speed on the C67x DSP and

perform the same types of operations (listed in Table 4−40) to accommodate

those memories. Table 4−40 shows the operation of program fetches pipeline

versus the operation of a data load.

Table 4−40. Program Memory Accesses Versus Data Load Accesses

Operation

Program Memory

Access Phase

Data Load

Access Phase

Compute address

PG

E1

Send address to memory

PS

E2

Memory read/write

PW

E3

Program memory: receive fetch packet at CPU boundary

Data load: receive data at CPU boundary

PR

E4

Program memory: send instruction to functional units

Data load: send data to register

DP

E5