B irp, Branch using an interrupt return pointer b irp – Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 133

Branch Using an Interrupt Return Pointer

B IRP

3-73

Instruction Set

SPRU733

Branch Using an Interrupt Return Pointer

B IRP

Syntax

B (.unit) IRP

.unit = .S2

Compatibility

C62x, C64x, C67x, and C67x+ CPU

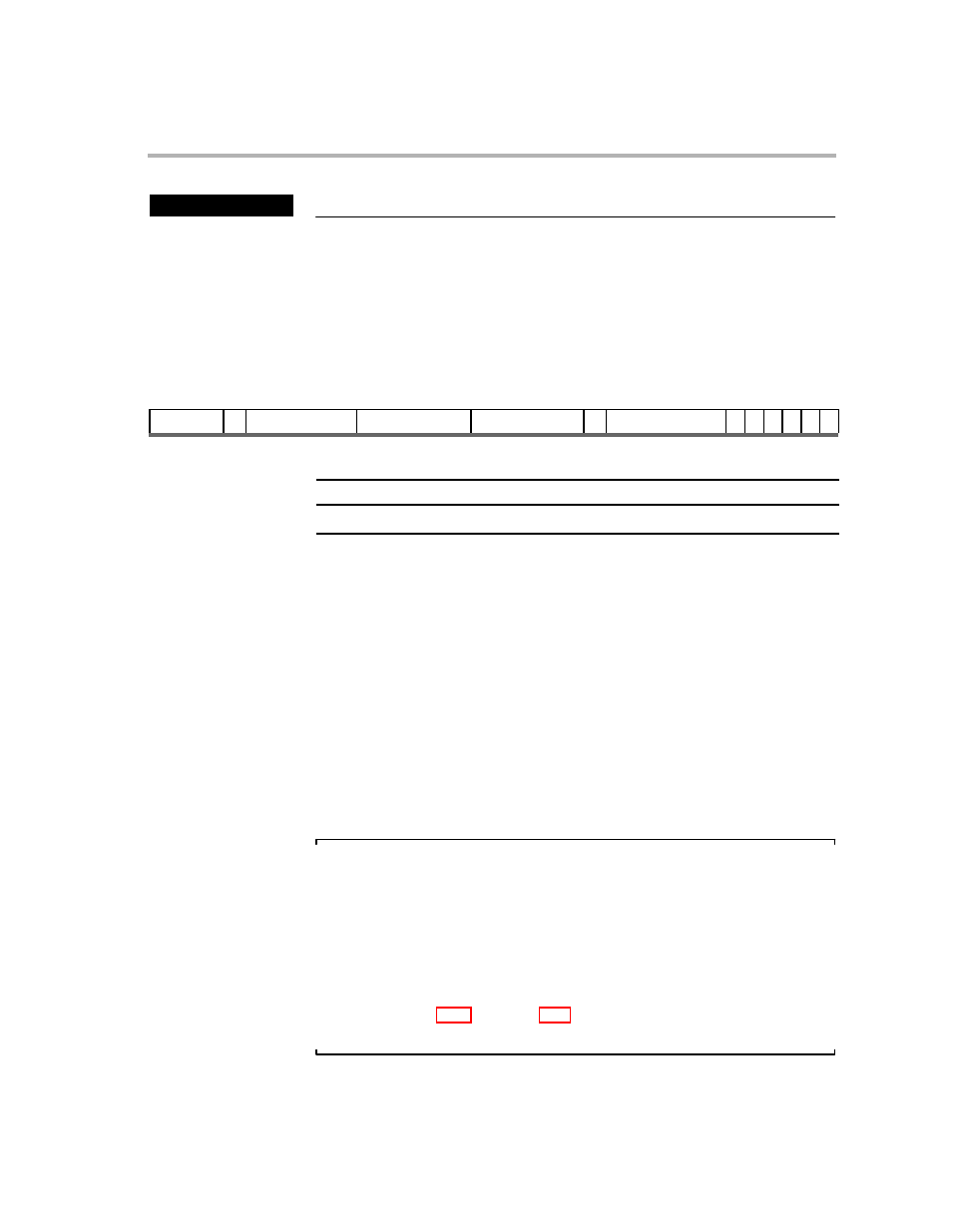

Opcode

31

29

28

27

23

22

18

17

13

12

11

6

5

4

3

2

1

0

creg

z

dst

0 0 1 1 0 0 0 0 0 0 x 0 0 0 0 1 1 1 0 0 0 s p

3

1

5

1

1

1

Opcode map field used...

For operand type...

Unit

src2

xsint

.S2

Description

IRP is placed in the program fetch counter (PFC). This instruction also moves

the PGIE bit value to the GIE bit. The PGIE bit is unchanged.

If two branches are in the same execute packet and are both taken, behavior

is undefined.

Two conditional branches can be in the same execute packet if one branch

uses a displacement and the other uses a register, IRP, or NRP. As long as only

one branch has a true condition, the code executes in a well-defined way.

Execution

if (cond)

IRP

→

PFC

else nop

Notes:

1) This instruction executes on .S2 only. PFC is the program fetch counter.

2) Refer to the chapter on interrupts for more information on IRP, PGIE, and

GIE.

3) The execute packets in the delay slots of a branch cannot be interrupted.

This is true regardless of whether the branch is taken.

4) See section 3.5.2 on page 3-18 for information on branching into the

middle of an execute packet.