7 interrupt flag register (ifr) – Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 44

Control Register File

CPU Data Paths and Control

2-18

SPRU733

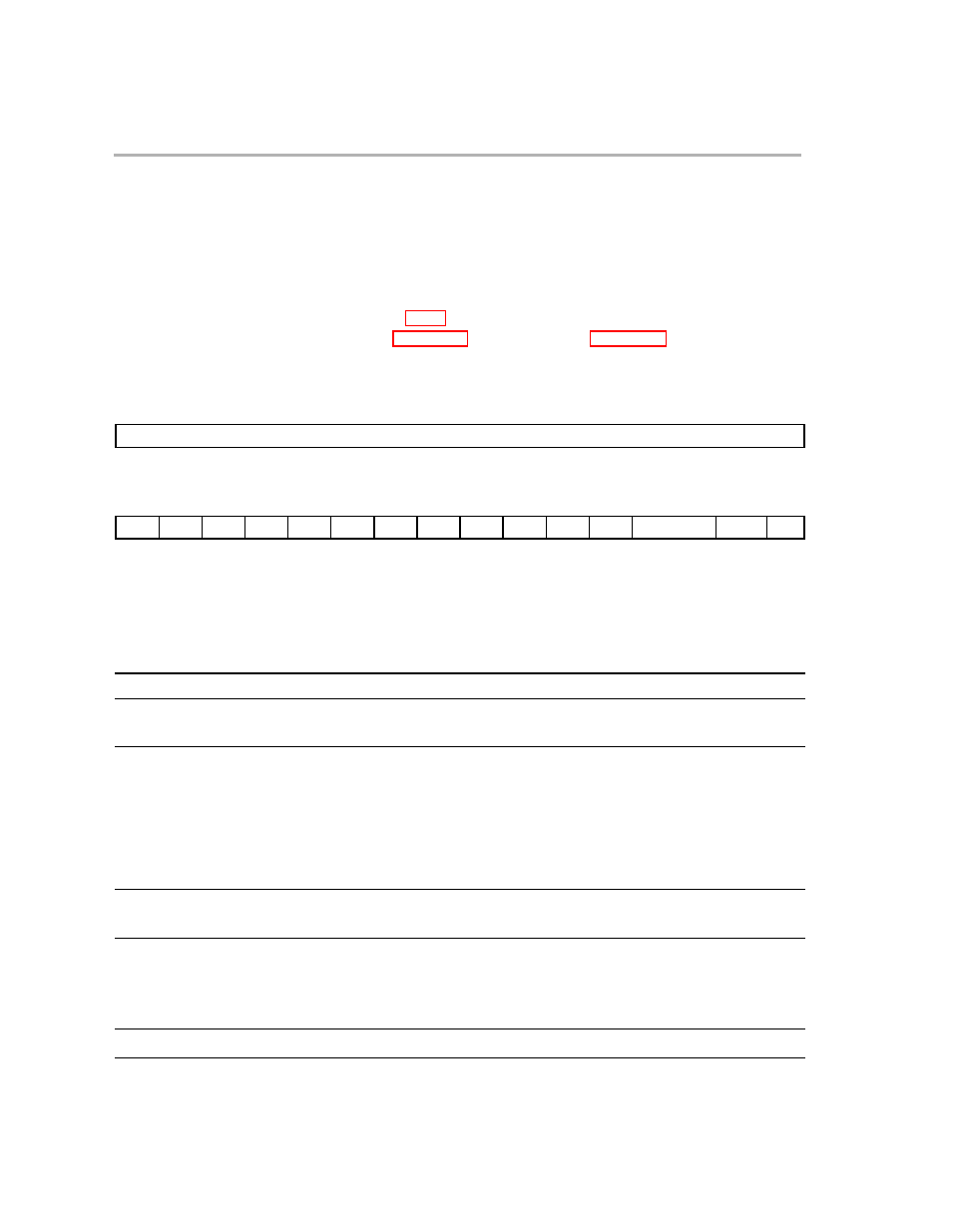

2.7.7 Interrupt Flag Register (IFR)

The interrupt flag register (IFR) contains the status of INT4−INT15 and NMI

interrupt. Each corresponding bit in the IFR is set to 1 when that interrupt

occurs; otherwise, the bits are cleared to 0. If you want to check the status of

interrupts, use the MVC instruction to read the IFR. (See the MVC instruction

description, page 3-180, for information on how to use this instruction.) The

IFR is shown in Figure 2−8 and described in Table 2−10.

Figure 2−8. Interrupt Flag Register (IFR)

31

16

Reserved

R-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

IF15 IF14 IF13 IF12 IF11 IF10

IF9

IF8

IF7

IF6

IF5

IF4

Reserved

NMIF

0

R-0

R-0

R-0

R-0

Legend: R = Readable by the MVC instruction; -n = value after reset

Table 2−10. Interrupt Flag Register (IFR) Field Descriptions

Bit

Field

Value Description

31−16 Reserved

0

Reserved. The reserved bit location is always read as 0. A value written to this

field has no effect.

15−4

IFn

Interrupt flag. Indicates the status of the corresponding maskable interrupt. An

interrupt flag may be manually set by setting the corresponding bit (ISn) in the

interrupt set register (ISR) or manually cleared by setting the corresponding bit

(ICn) in the interrupt clear register (ICR).

0

Interrupt has not occurred.

1

Interrupt has occurred.

3−2

Reserved

0

Reserved. The reserved bit location is always read as 0. A value written to this

field has no effect.

1

NMIF

Nonmaskable interrupt flag.

0

Interrupt has not occurred.

1

Interrupt has occurred.

0

0

0

Reset interrupt flag.