Lddw – Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 188

LDDW

Load Doubleword From Memory With an Unsigned Constant Offset or Register Offset

3-128

Instruction Set

SPRU733

Load Doubleword From Memory With an Unsigned Constant Offset

or Register Offset

LDDW

Syntax

Register Offset

LDDW (.unit) *+baseR[offsetR], dst

Unsigned Constant Offset

LDDW (.unit) *+baseR[ucst5], dst

.unit = .D1 or .D2

Compatibility

C67x and C67x+ CPU

Opcode

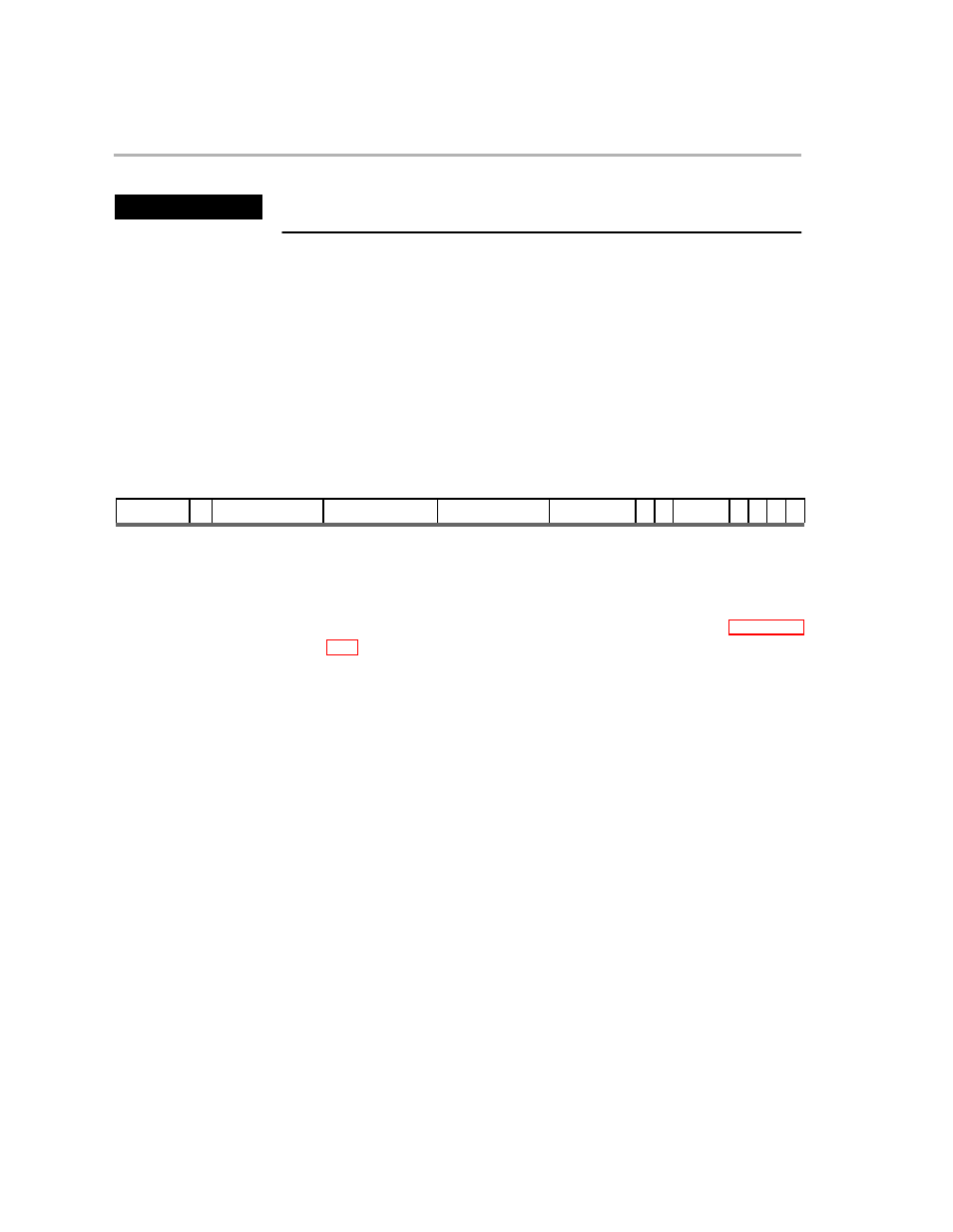

31

29

28

27

23

22

18

17

13

12

9

8

7

6

4

3

2

1

0

creg

z

dst

baseR

offsetR/ucst5

mode

1 y 1 1 0 0 1 s p

3

1

5

5

5

4

1

1

1

Description

Loads a doubleword from memory into a register pair dst_o:dst_e. Table 3−11

(page 3-33) describes the addressing generator options. The memory

address is formed from a base address register (baseR) and an optional offset

that is either a register (offsetR) or a 5-bit unsigned constant (ucst5).

Both offsetR and baseR must be in the same register file and on the same side

as the .D unit used. The y bit in the opcode determines the .D unit and the regis-

ter file used: y = 0 selects the .D1 unit and the baseR and offsetR from the

A register file, and y = 1 selects the .D2 unit and baseR and offsetR from the

B register file. The s bit determines the register file into which the dst is loaded:

s = 0 indicates that dst is in the A register file, and s = 1 indicates that dst is

in the B register file. The r bit has a value of 1 for the LDDW instruction. The

dst field must always be an even value because the LDDW instruction loads

register pairs. Therefore, bit 23 is always zero.

The offsetR/ucst5 is scaled by a left-shift of 3 to correctly represent double-

words. After scaling, offsetR/ucst5 is added to or subtracted from baseR. For

the preincrement, predecrement, positive offset, and negative offset address

generator options, the result of the calculation is the address to be accessed

in memory. For postincrement or postdecrement addressing, the shifted value

of baseR before the addition or subtraction is the address to be accessed in

memory.