Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 311

Subtract Two Signed Integers Without Saturation

SUB

3-251

Instruction Set

SPRU733

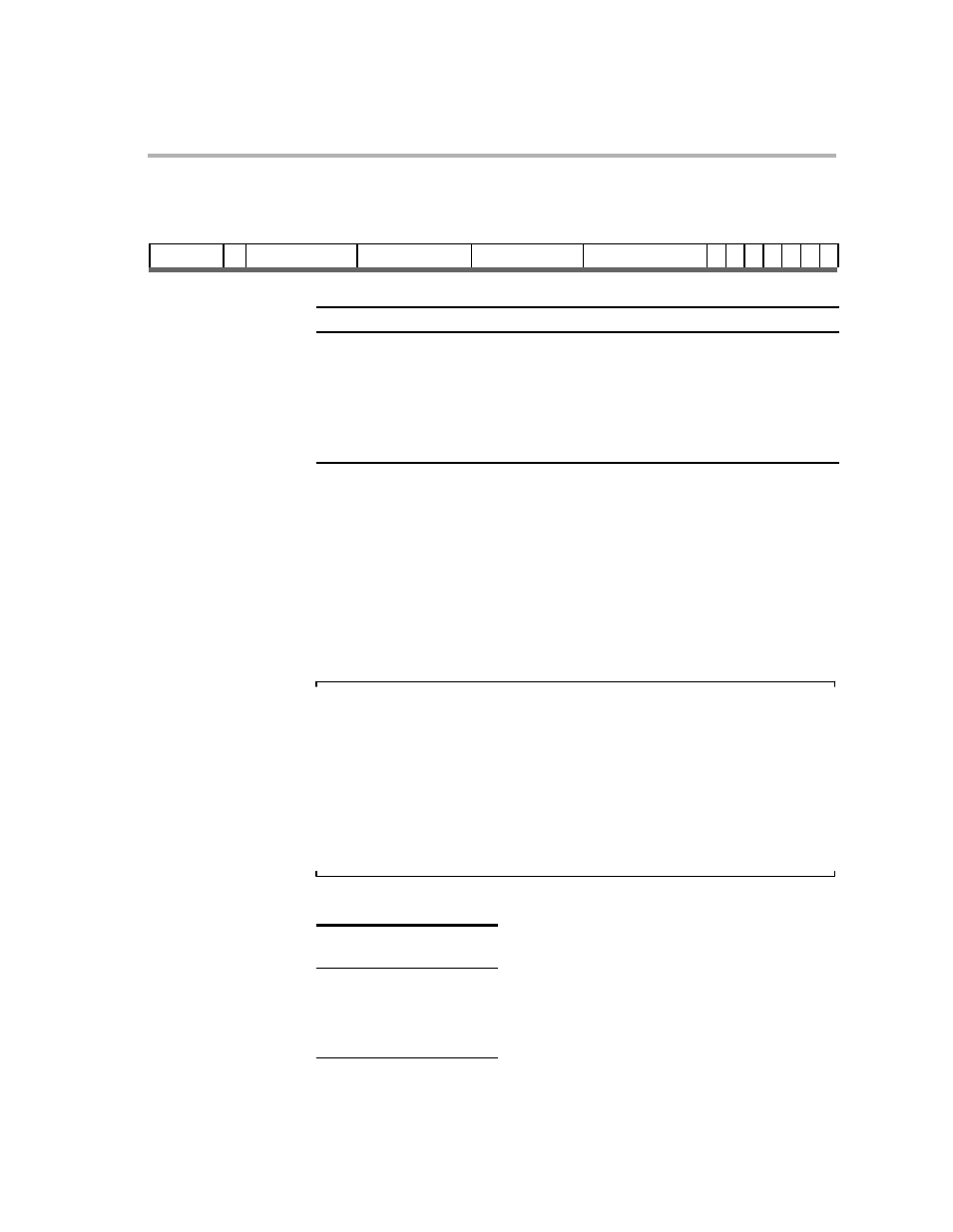

Opcode

.D unit

31

29

28

27

23

22

18

17

13

12

7

6

5

4

3

2

1

0

creg

z

dst

src2

src1

op

1 0 0 0 0 s p

3

1

5

5

5

6

1

1

Opcode map field used...

For operand type...

Unit

Opfield

src2

src1

dst

sint

sint

sint

.D1, .D2

01 0001

src2

src1

dst

sint

ucst5

sint

.D1, .D2

01 0011

Description for .D1, .D2 Opcodes

src1 is subtracted from src2. The result is placed in dst.

Execution for .D1, .D2 Opcodes

if (cond)

src2 − src1

→

dst

else nop

Note:

Subtraction with a signed constant on the .L and .S units allows either the first

or the second operand to be the signed 5-bit constant.

SUB (.unit) src1, scst5, dst is encoded as ADD (.unit) −scst5, src2, dst where

the src1 register is now src2 and scst5 is now −scst5.

However, the .D unit provides only the second operand as a constant since

it is an unsigned 5-bit constant. ucst5 allows a greater offset for addressing

with the .D unit.

Pipeline

Stage

E1

Read

src1, src2

Written

dst

Unit in use

.L, .S, or .D

Pipeline