4 setting the reset interrupt flag – Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 414

Interrupt Detection and Processing

5-19

Interrupts

SPRU733

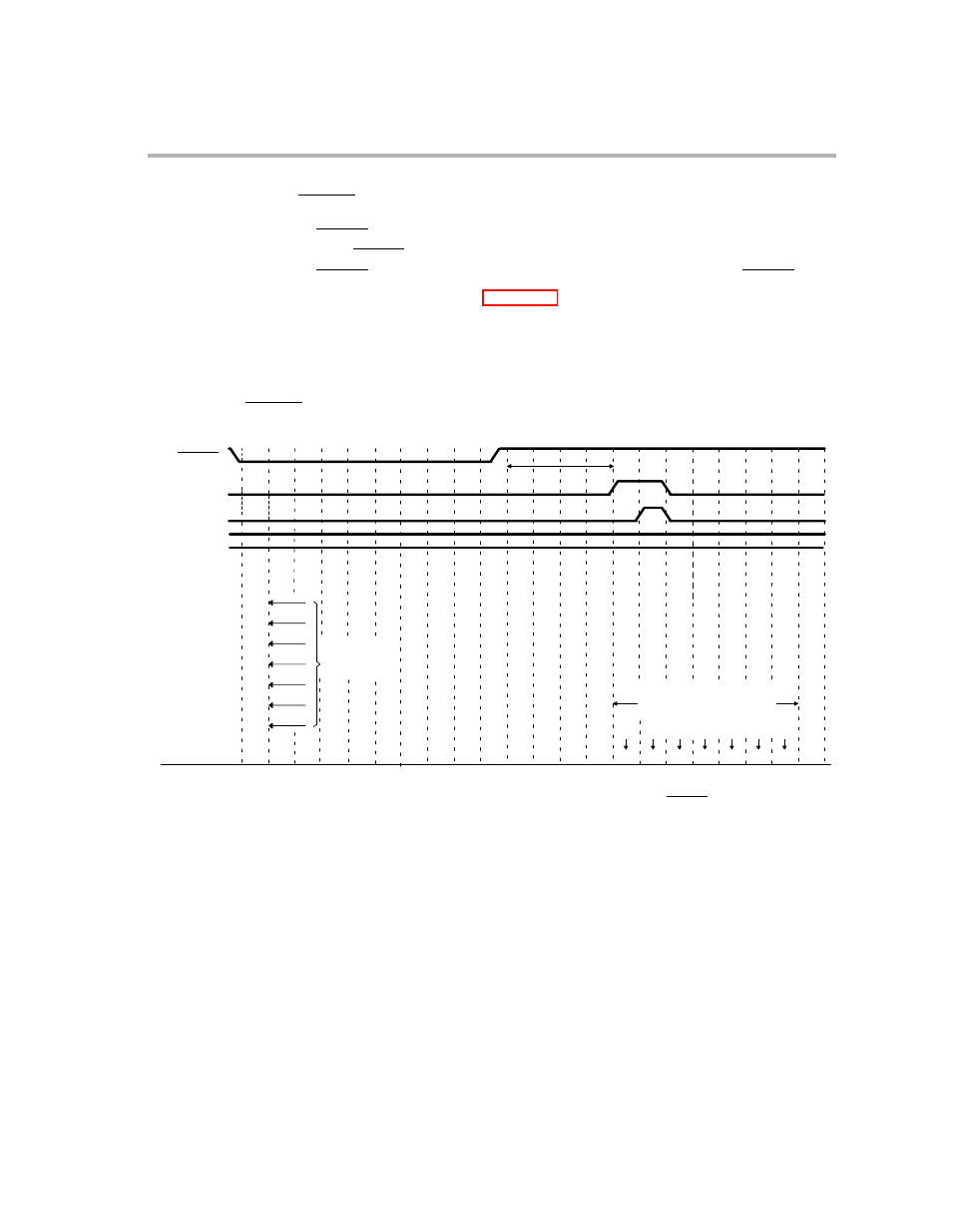

5.4.4 Setting the RESET Interrupt Flag

RESET must be held low for a minimum of 10 clock cycles. Four clock cycles

after RESET goes high, processing of the reset vector begins. The flag for

RESET (IF0) in the IFR is set by the low-to-high transition of the RESET signal

on the CPU boundary. In Figure 5−5, IF0 is set during CPU cycle 15. This tran-

sition is detected on a clock-cycle by clock-cycle basis and is not affected by

memory stalls that might extend a CPU cycle.

Figure 5−5. RESET Interrupt Detection and Processing: Pipeline Operation

Reset ISFP

n+7

n+6

Pipeline flush

E1

DC

DP

PR

PW

PS

PG

PG

PS

PW

PR

DP

DC

E1

n+5

n+4

n+3

n+2

n+1

n

Execute

packet

INUM

IACK

IF0

RESET

Clock cycle

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Cycles 15 −21:

Nonreset interrupt

processing is disabled

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

{

}

CPU cycle

at pin

0

PG

PS

PW

PR

DP

DC

E2

E1

0

0

0

0

0

22

21

20

19

18

0

22

21

20

19

18

†

IF0 is set on the next CPU cycle boundary after a 4-clock cycle delay after the rising edge of RESET.

‡

After this point, interrupts are still disabled. All nonreset interrupts are disabled when NMIE = 0. All maskable interrupts are

disabled when GIE = 0.