5 branch instructions, See section 4.2.5 for more information on branches – Texas Instruments TMS320C67X/C67X+ DSP User Manual

Page 354

Pipeline Execution of Instruction Types

Pipeline

4-22

SPRU733

4.2.5 Branch Instructions

Although branch takes one execute phase, there are five delay slots between

the execution of the branch and execution of the target code (see Table 4−7).

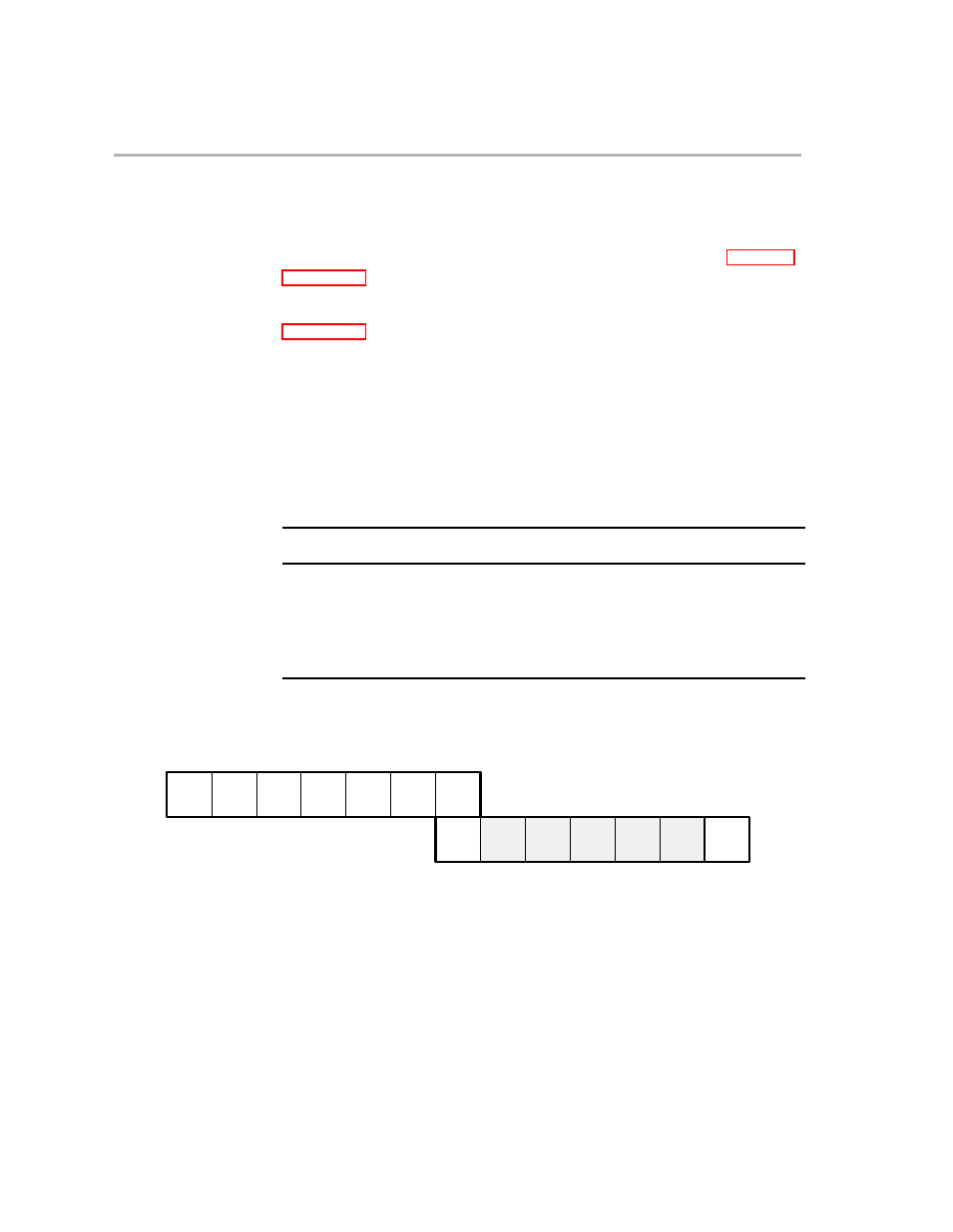

Figure 4−16 shows the pipeline phases used by the branch instruction and

branch target code. The delay slots are shaded.

Figure 4−17 shows a branch instruction execution block diagram. If a branch

is in the E1 phase of the pipeline (in the .S2 unit in the figure), its branch target

is in the fetch packet that is in PG during that same cycle (shaded in the figure).

Because the branch target has to wait until it reaches the E1 phase to begin

execution, the branch takes five delay slots before the branch target code

executes.

Table 4−7. Branch Instruction Execution

Pipeline Stage

E1

PS

PW

PR

DP

DC

E1

Read

src2

Written

Branch Taken

n

Unit in use

.S2

Figure 4−16. Branch Instruction Phases

Branch

target

PG

PS

PW

PR

DP

DC

E1

PG

PS

PW

PR

DP

DC

E1

5 delay slots