Hardware, Machine instructions – Renesas 4514 User Manual

Page 96

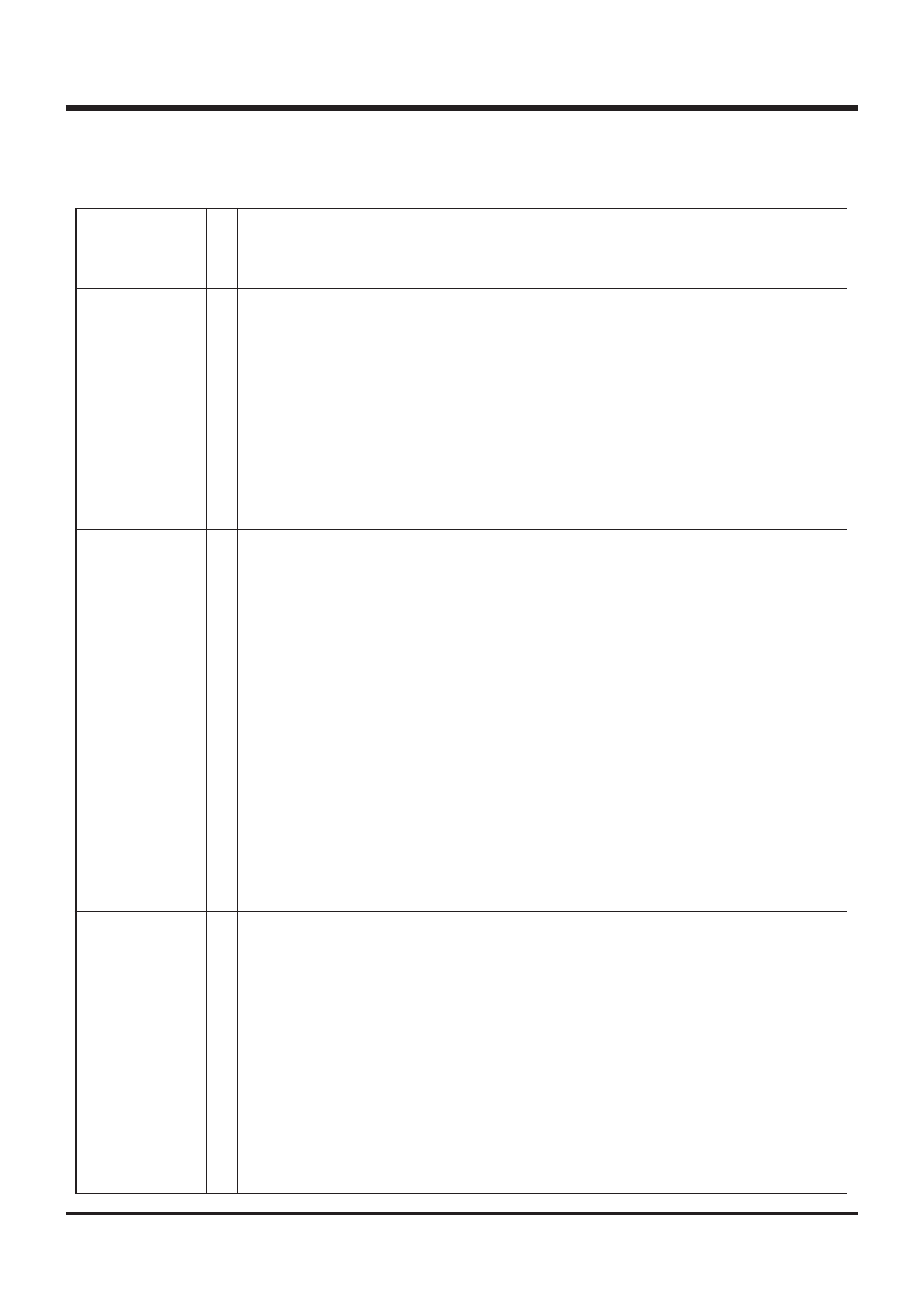

Skip condition

Datailed description

Carry flag CY

4513/4514 Group User’s Manual

HARDWARE

1-83

MACHINE INSTRUCTIONS

–

–

–

–

–

(SIOF) = 1

–

–

–

–

–

–

(ADF) = 1

–

–

–

–

–

(P) = 1

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

Transfers the contents of serial I/O register SI to registers A and B.

Transfers the contents of registers A and B to serial I/O register SI.

Transfers the contents of serial I/O mode register J1 to register A.

Transfers the contents of register A to serial I/O mode register J1.

Clears (0) to SIOF flag and starts serial I/O.

Skips the next instruction when the contents of SIOF flag is “1.”

After skipping, clears (0) to SIOF flag.

Transfers the high-order 8 bits of the contents of register AD to registers A and B.

Transfers the low-order 2 bits of the contents of register AD to the high-order 2 bits of the contents of regis-

ter A. Simultaneously, the low-order 2 bits of the contents of the register A is “0.”

Transfers the contents of registers A and B to the comparator register at the comparator mode.

Transfers the contents of the A-D control register Q1 to register A.

Transfers the contents of register A to the A-D control register Q1.

Clears the ADF flag, and the A-D conversion at the A-D conversion mode or the comparator operation at the

comparator mode is started.

Skips the next instruction when the contents of ADF flag is “1”.

After skipping, clears (0) the contents of ADF flag.

Transfers the contents of the A-D control register Q2 to register A.

Transfers the contents of register A to the A-D control register Q2.

No operation

Puts the system in RAM back-up state by executing the POF instruction after executing the EPOF instruction.

Makes the immediate POF instruction valid by executing the EPOF instruction.

Skips the next instruction when P flag is “1”. After skipping, P flag remains unchanged.

Operates the watchdog timer and initializes the watchdog timer flag WDF1.

Transfers the contents of the clock control register MR to register A.

Transfers the contents of register A to the clock control register MR.

Transfers the contents of the voltage comparator control register Q3 to register A.

Transfers the contents of the high-order 2 bits of register A to the high-order 2 bits of voltage comparator

control register Q3, and the comparison result of the voltage comparator is transferred to the low-order 2 bits

of the register Q3.