Application – Renesas 4514 User Manual

Page 118

APPLICATION

2.2 Interrupts

2-15

4513/4514 Group User’s Manual

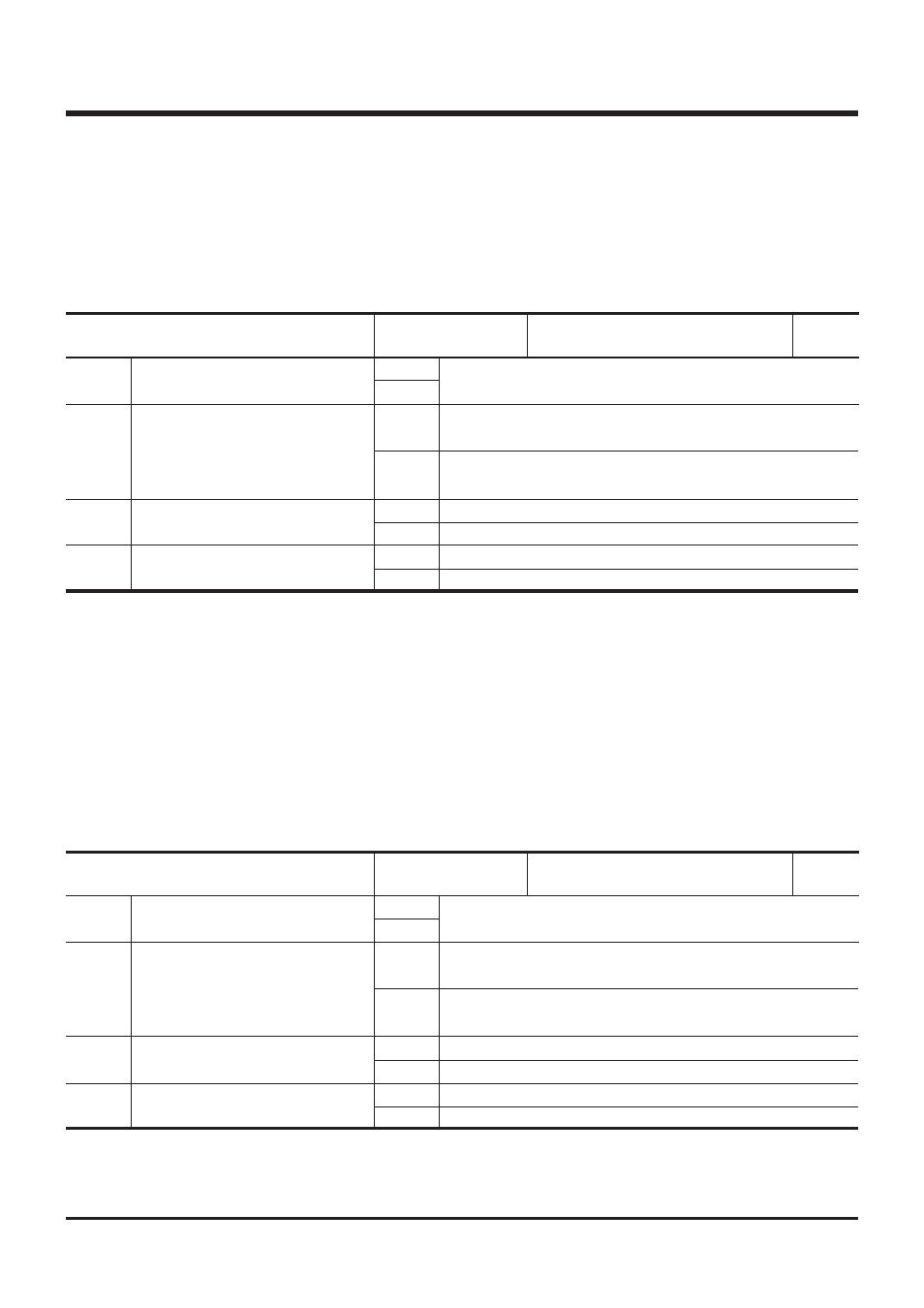

Interrupt control register I1

at reset : 0000

2

at RAM back-up : state retained

R/W

This bit has no function, but read/write is enabled.

Falling waveform (“L” level of INT0 pin is recognized

with the SNZI0 instruction)/“L” level

Rising waveform (“H” level of INT0 pin is recognized

with the SNZI0 instruction)/“H” level

One-sided edge detected

Both edges detected

Disabled

Enabled

Not used

Interrupt valid waveform for INT0

pin/return level selection bit

(Note 2)

INT0 pin edge detection circuit

control bit

INT0 pin

timer 1 control enable bit

0

1

0

1

0

1

0

1

I1

3

I1

2

I1

1

I1

0

Notes 1: “R” represents read enabled, and “W” represents write enabled.

2: When the contents of I1

2

is changed, the external interrupt request flag EXF0 may be set.

Accordingly, clear EXF0 flag with the SNZ0 instruction.

(5)

Interrupt control register I1

The INT0 pin timer 1 control enable bit is assigned to bit 0, INT0 pin edge detection circuit control

bit is assigned to bit 1, and interrupt valid waveform for INT0 pin/return level selection bit is assigned

to bit 2.

Set the contents of this register through register A with the TI1A instruction.

In addition, the TAI1 instruction can be used to transfer the contents of register I1 to register A.

Table 2.2.3 shows the interrupt control register I1.

Table 2.2.3 Interrupt control register I1

(6)

Interrupt control register I2

The INT1 pin timer 3 control enable bit is assigned to bit 0, the INT1 pin edge detection circuit control

bit is assigned to bit 1 and the interrupt valid waveform for INT1 pin/return level selection bit is

assigned to bit 2.

Set the contents of this register through register A with the TI2A instruction.

In addition, the TAI2 instruction can be used to transfer the contents of register I2 to register A.

Table 2.2.4 shows the interrupt control register I2.

Table 2.2.4 Interrupt control register I2

Interrupt control register I2

at reset : 0000

2

at RAM back-up : state retained

R/W

This bit has no function, but read/write is enabled.

Falling waveform (“L” level of INT1 pin is recognized

with the SNZI1 instruction)/“L” level

Rising waveform (“H” level of INT1 pin is recognized

with the SNZI1 instruction)/“H” level

One-sided edge detected

Both edges detected

Disabled

Enabled

Not used

Interrupt valid waveform for INT1

pin/return level selection bit

(Note 2)

INT1 pin edge detection circuit

control bit

INT1 pin

timer 3 control enable bit

0

1

0

1

0

1

0

1

I2

3

I2

2

I2

1

I2

0

Notes 1: “R” represents read enabled, and “W” represents write enabled.

2: When the contents of I2

2

is changed, the external interrupt request flag EXF1 may be set.

Accordingly, clear EXF1 flag with the SNZ1 instruction.