Interrupt function, Hardware, Function block operations – Renesas 4514 User Manual

Page 35: 1) interrupt enable flag (inte), 2) interrupt enable bit, 3) interrupt request flag

1-22

HARDWARE

4513/4514 Group User’s Manual

FUNCTION BLOCK OPERATIONS

INTERRUPT FUNCTION

The interrupt type is a vectored interrupt branching to an individual

address (interrupt address) according to each interrupt source. An

interrupt occurs when the following 3 conditions are satisfied.

• An interrupt activated condition is satisfied (request flag = “1”)

• Interrupt enable bit is enabled (“1”)

• Interrupt enable flag is enabled (INTE = “1”)

Table 3 shows interrupt sources. (Refer to each interrupt request

flag for details of activated conditions.)

(1) Interrupt enable flag (INTE)

The interrupt enable flag (INTE) controls whether the every inter-

rupt enable/disable. Interrupts are enabled when INTE flag is set to

“1” with the EI instruction and disabled when INTE flag is cleared to

“0” with the DI instruction. When any interrupt occurs, the INTE flag

is automatically cleared to “0,” so that other interrupts are disabled

until the EI instruction is executed.

(2) Interrupt enable bit

Use an interrupt enable bit of interrupt control registers V1 and V2

to select the corresponding interrupt or skip instruction.

Table 4 shows the interrupt request flag, interrupt enable bit and

skip instruction.

Table 5 shows the interrupt enable bit function.

(3) Interrupt request flag

When the activated condition for each interrupt is satisfied, the cor-

responding interrupt request flag is set to “1.” Each interrupt

request flag is cleared to “0” when either;

• an interrupt occurs, or

• the next instruction is skipped with a skip instruction.

Each interrupt request flag is set when the activated condition is

satisfied even if the interrupt is disabled by the INTE flag or its in-

terrupt enable bit. Once set, the interrupt request flag retains set

until a clear condition is satisfied.

Accordingly, an interrupt occurs when the interrupt disable state is

released while the interrupt request flag is set.

If more than one interrupt request flag is set when the interrupt dis-

able state is released, the interrupt priority level is as follows

shown in Table 3.

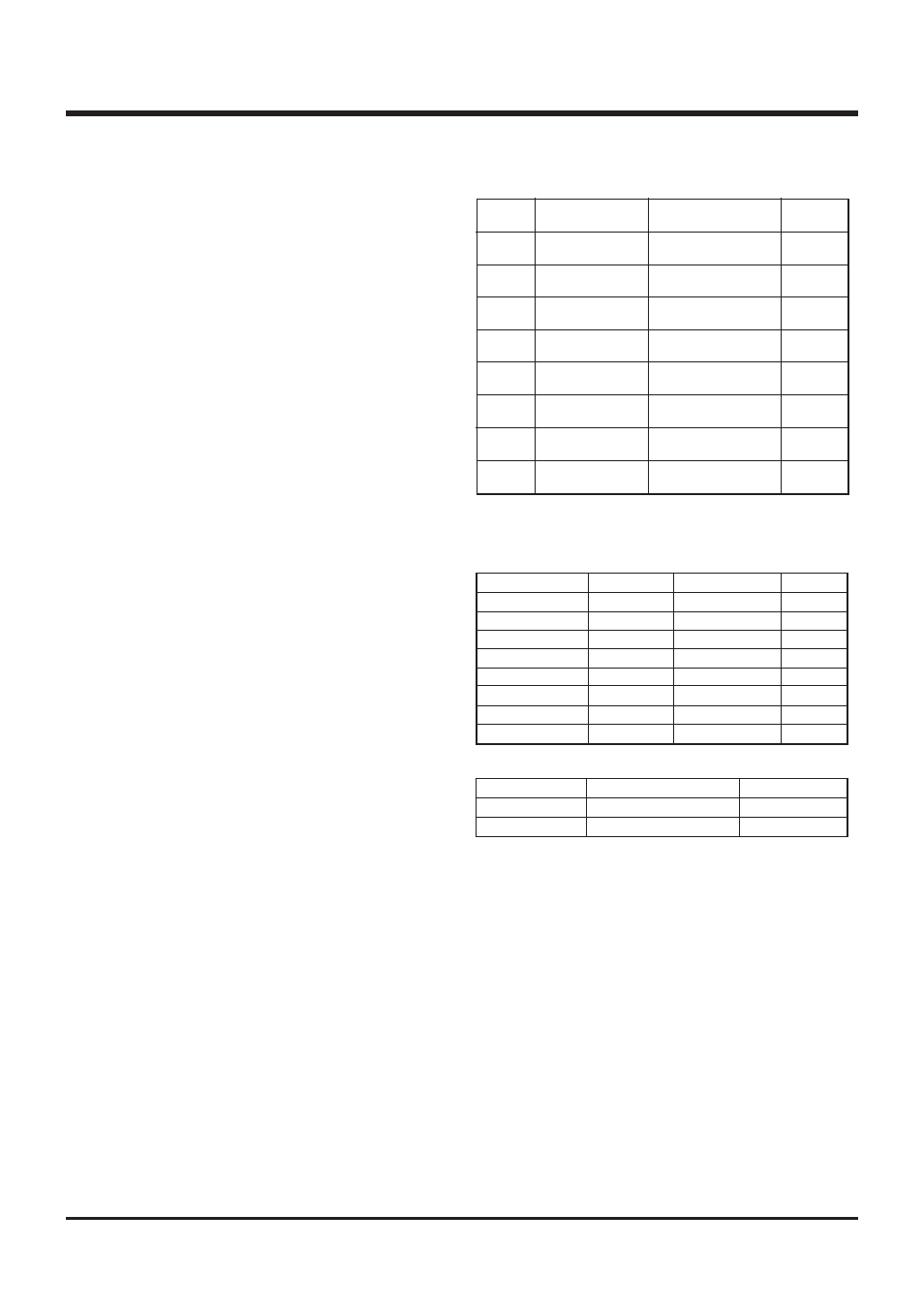

Table 3 Interrupt sources

Activated condition

Level change of

INT0 pin

Level change of

INT1 pin

Timer 1 underflow

Timer 2 underflow

Timer 3 underflow

Timer 4 underflow

Completion of

A-D conversion

Completion of

serial I/O transfer

Priority

level

1

2

3

4

5

6

7

8

Interrupt name

External 0 interrupt

External 1 interrupt

Timer 1 interrupt

Timer 2 interrupt

Timer 3 interrupt

Timer 4 interrupt

A-D interrupt

Serial I/O interrupt

Request flag

EXF0

EXF1

T1F

T2F

T3F

T4F

ADF

SIOF

Interrupt name

External 0 interrupt

External 1 interrupt

Timer 1 interrupt

Timer 2 interrupt

Timer 3 interrupt

Timer 4 interrupt

A-D interrupt

Serial I/O interrupt

Table 5 Interrupt enable bit function

Occurrence of interrupt

Enabled

Disabled

Skip instruction

Invalid

Valid

Interrupt enable bit

1

0

Interrupt

address

Address 0

in page 1

Address 2

in page 1

Address 4

in page 1

Address 6

in page 1

Address 8

in page 1

Address A

in page 1

Address C

in page 1

Address E

in page 1

Table 4 Interrupt request flag, interrupt enable bit and skip in-

struction

Skip instruction

SNZ0

SNZ1

SNZT1

SNZT2

SNZT3

SNZT4

SNZAD

SNZSI

Enable bit

V1

0

V1

1

V1

2

V1

3

V2

0

V2

1

V2

2

V2

3