2 related registers, Application, 4 serial i/o – Renesas 4514 User Manual

Page 144

APPLICATION

2.4 Serial I/O

2-41

4513/4514 Group User’s Manual

2.4.2 Related registers

(1)

Serial I/O register SI

Serial I/O register SI is the 8-bit data transfer serial/parallel conversion register. Data can be set to

register SI through registers A and B with the TSIAB instruction.

(2)

Serial I/O mode register J1

Serial I/O synchronous clock selection bit is assigned to bit 0, serial I/O port selection bit is assigned

to bit 1 and serial I/O internal clock dividing ratio selection bit is assigned to bit 2.

Set the contents of this register through register A with the TJ1A instruction. The TAJ1 instruction

can be used to transfer the contents of register J1 to register A.

Table 2.4.1 shows the serial I/O mode register J1.

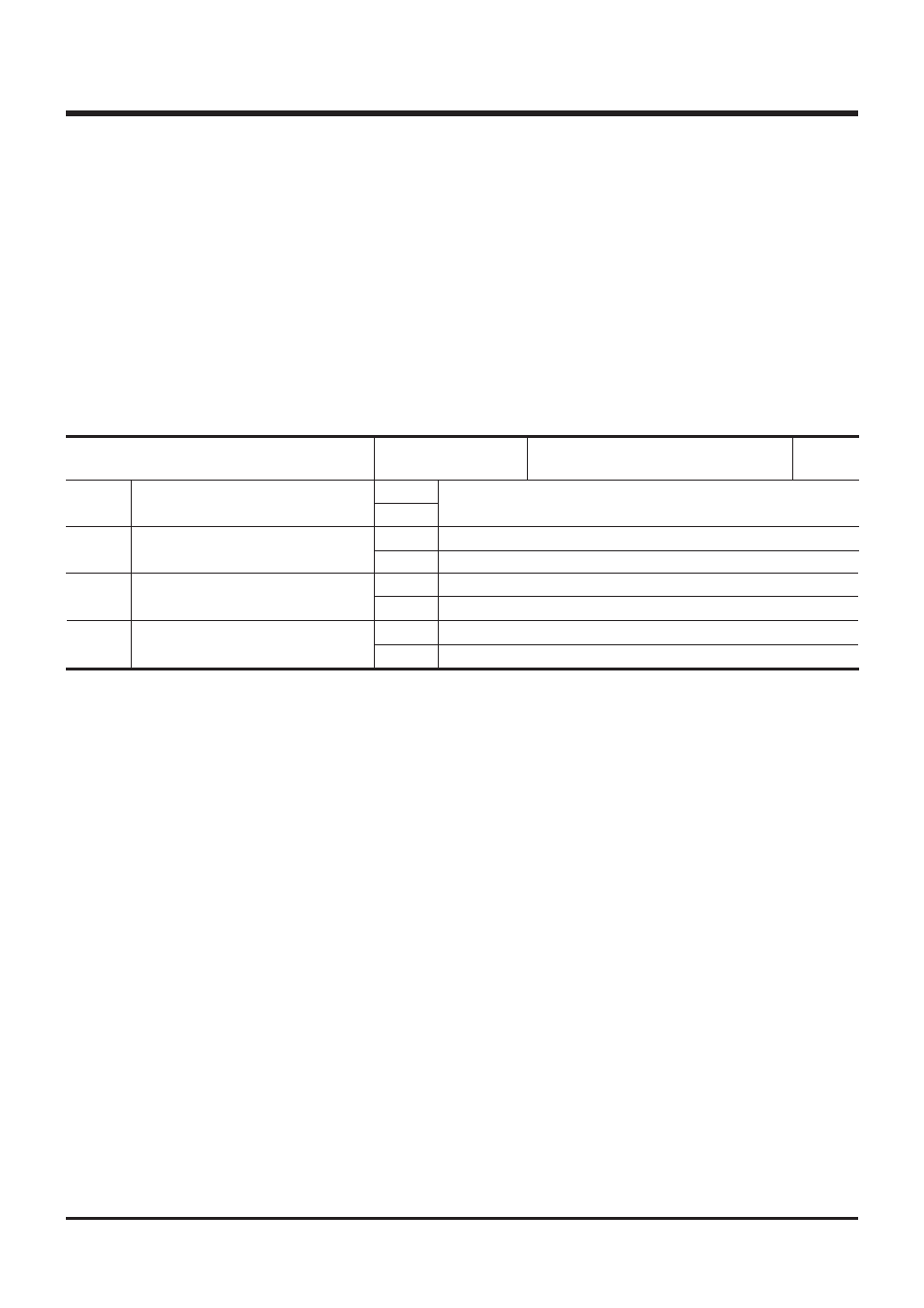

Table 2.4.1 Serial I/O mode register J1

Note: “R” represents read enabled, and “W” represents write enabled.

(3)

Serial I/O transmission/reception completion flag (SIOF)

Serial I/O transmission/reception completion flag (SIOF) is set to “1” when serial data transmission

or reception completes. The state of SIOF flag can be examined with the skip instruction (SNZSI).

Serial I/O mode register J1

at reset : 0000

2

at RAM back-up : state retained

R/W

This bit has no function, but read/write is enabled.

Instruction clock signal divided by 8

Instruction clock signal divided by 4

Input ports P2

0

, P2

1

, P2

2

selected

Serial I/O ports S

CK

, S

OUT

, S

IN

/input ports P2

0

, P2

1

, P2

2

selected

External clock

Internal clock (instruction clock divided by 4 or 8)

Not used

Serial I/O internal clock dividing

ratio selection bit

Serial I/O port selection bit

Serial I/O synchronous clock

selection bit

J1

3

J1

2

J1

1

J1

0

0

1

0

1

0

1

0

1