Application, 1 i/o pins – Renesas 4514 User Manual

Page 109

2-6

APPLICATION

2.1 I/O pins

4513/4514 Group User’s Manual

(4)

Direction register FR0 (The 4513 Group does not have this register.)

Register FR0 is used to switch to input/output of P5

0

–P5

3

.

Set the contents of this register through register A with the TFR0A instruction.

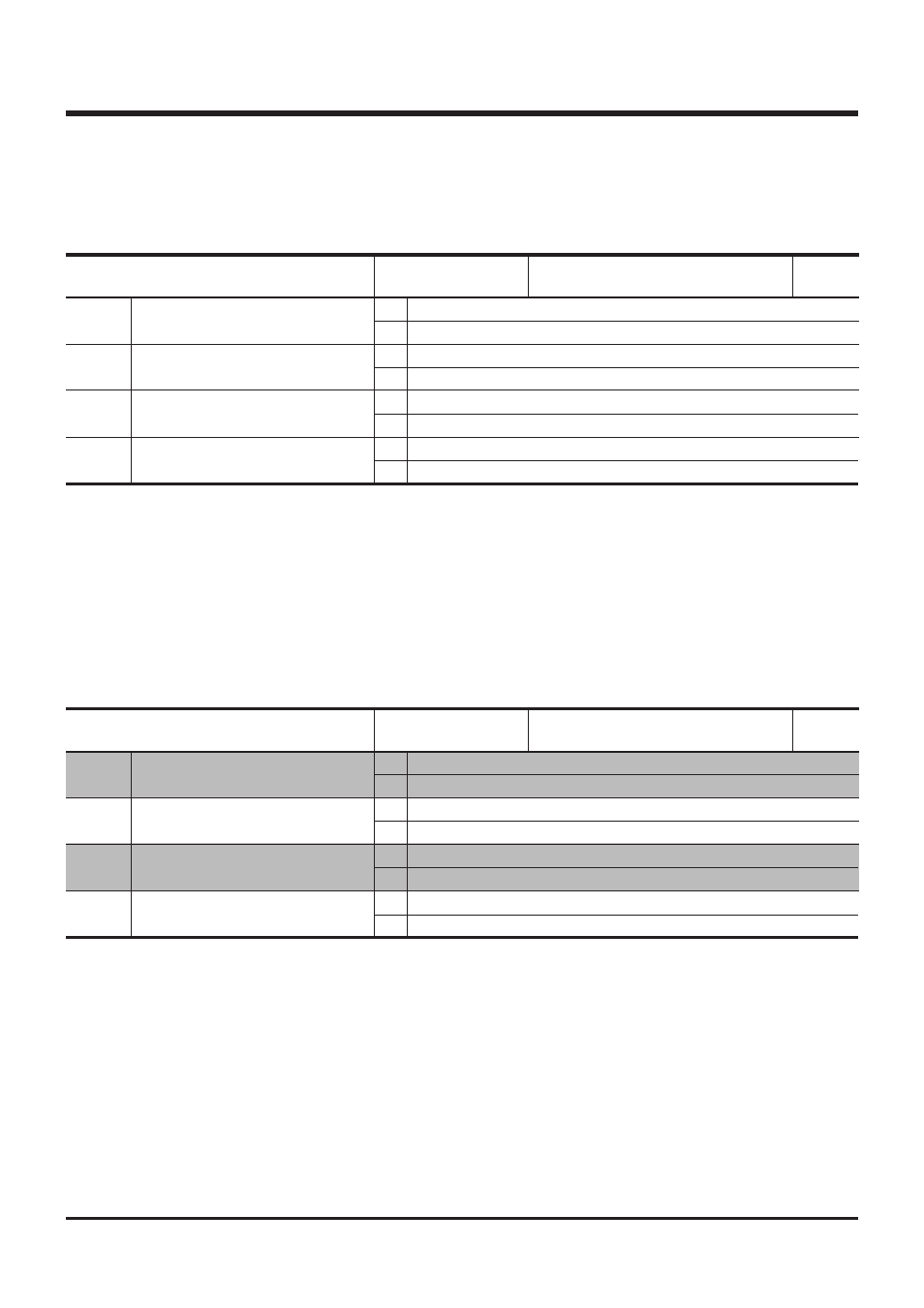

Table 2.1.4 shows the direction register FR0.

Table 2.1.4 Direction register FR0

Direction register FR0 (Note 2)

at reset : 0000

2

at RAM back-up : state retained

W

Port P5

3

input

Port P5

3

output

Port P5

2

input

Port P5

2

output

Port P5

1

input

Port P5

1

output

Port P5

0

input

Port P5

0

output

Port P5

3

input/output control bit

Port P5

2

input/output control bit

Port P5

1

input/output control bit

Port P5

0

input/output control bit

0

1

0

1

0

1

0

1

Notes 1: “W” represents write enabled.

2: The 4513 Group does not have register FR0.

FR0

3

FR0

2

FR0

1

FR0

0

(5)

Timer control register W6

D

6

/CNTR0 function selection bit is assigned to bit 0, D

7

/CNTR1 function selection bit is assigned to

bit 2.

Set the contents of this register through register A with the TW6A instruction.

The contents of register W6 is transferred to register A with the TAW6 instruction.

Table 2.1.5 shows the timer control register W6.

Table 2.1.5 Timer control register W6

Timer control register W6

at reset : 0000

2

at RAM back-up : state retained

R/W

Timer 3 underflow signal output divided by 2

CNTR1 output control by timer 4 underflow signal divided by 2

D

7

(I/O)/CNTR1 input

CNTR1 I/O/D

7

(input)

Timer 1 underflow signal output divided by 2

CNTR0 output control by timer 2 underflow signal divided by 2

D

6

(I/O)/CNTR0 input

CNTR0 I/O/D

6

(input)

CNTR1 output control bit

D

7

/CNTR1 function selection bit

CNTR0 output control bit

D

6

/CNTR0 function selection bit

0

1

0

1

0

1

0

1

Notes 1: “R” represents read enabled, and “W” represents write enabled.

2: When setting ports, W6

3

and W6

1

are not used.

W6

3

W6

2

W6

1

W6

0