Scrub control register, Scrub control register -19 – Motorola MVME1X7P User Manual

Page 267

Programming Model

http://www.motorola.com/computer/literature

4-19

4

cleared during normal system operation. DERC also

allows the write portion of a read-modify-write to

complete regardless of whether or not there was a multiple

bit error during the read portion of the read-modify-write.

DERC also affects scrub cycles.

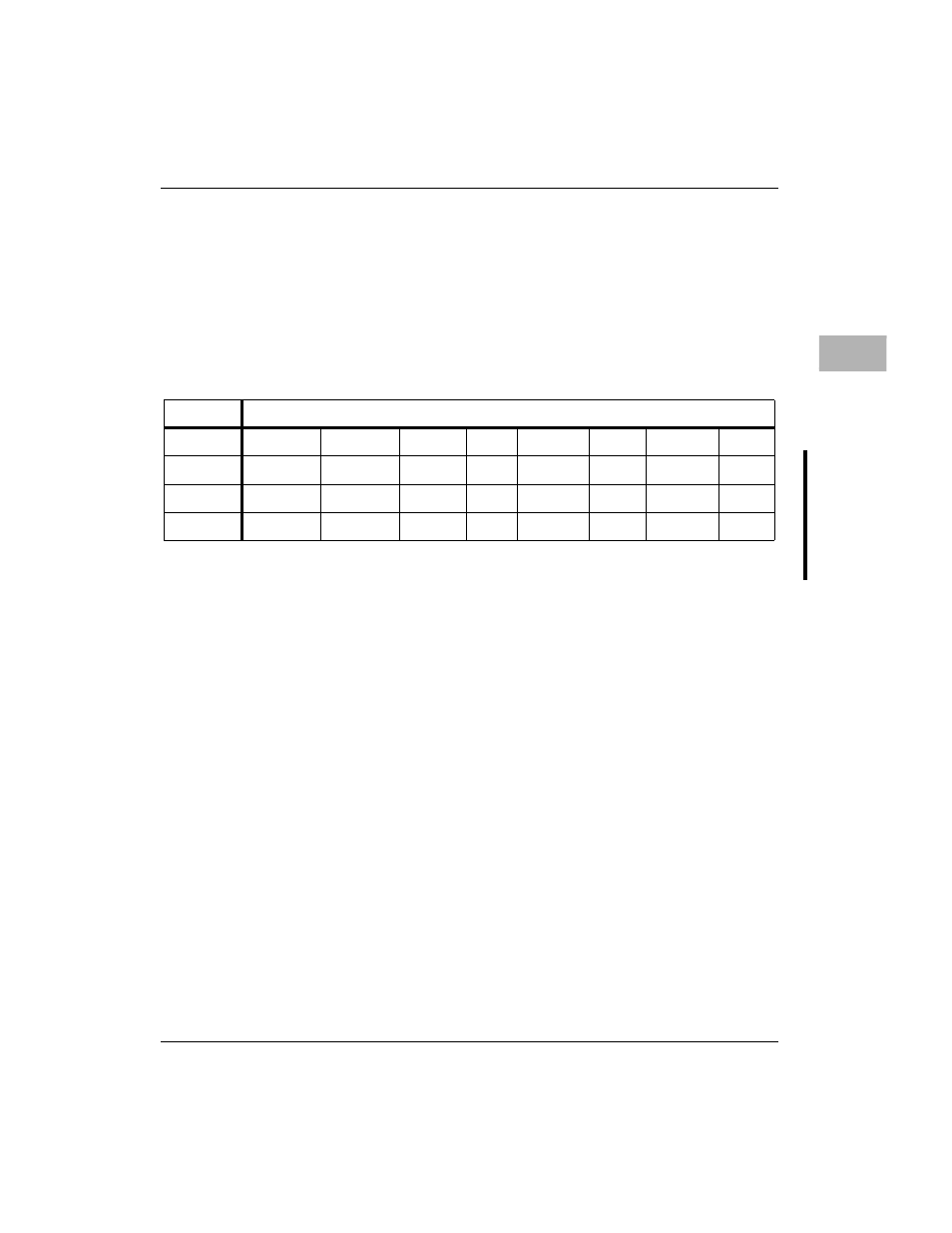

Scrub Control Register

RWB0

RWB0 is a general-purpose read/write bit.

SBEIEN

Setting SBEIEN causes the logging of a single-bit error to

create a true pulse on the INT signal pin.

SCRBEN This control bit enables the scrubber to operate. When

SCRBEN is set, the MCECC sector immediately

performs a scrub of the entire DRAM array. When the

scrub is complete, if software has cleared SCRBEN, then

scrubbing is not done again, until software sets the

SCRBEN bit. If software has not cleared the SCRBEN bit,

then when the amount of time indicated in the Scrub

Period (SBPD) register expires, the MCECC sector scrubs

the DRAM array again. It continues to perform scrubs of

the entire DRAM array at the frequency indicated in the

SBPD register. The scrubber does not start a new scrub

once the SCRBEN bit is cleared. The time between scrubs

is approximately two seconds times the value stored in the

SBPD register. Note that a power-up, local, or software

reset stops the scrubber.

ADR/SIZ

1st $FFF43024/2nd $FFF43124 (8-bits)

BIT

31

30

29

28

27

26

25

24

NAME

0

0

0

SCRB SCRBEN 0

SBEIEN

RWB0

OPER

R

R

R

R

R/W

R

R/W

R/W

RESET

0 PLS

0 PLS

0 PLS

0 PLS 0 PLS

X

0 PLS

0 PLS