Vmebus interrupter vector register, Mpu status and dma interrupt count register – Motorola MVME1X7P User Manual

Page 152

2-62

Computer Group Literature Center Web Site

VMEchip2

2

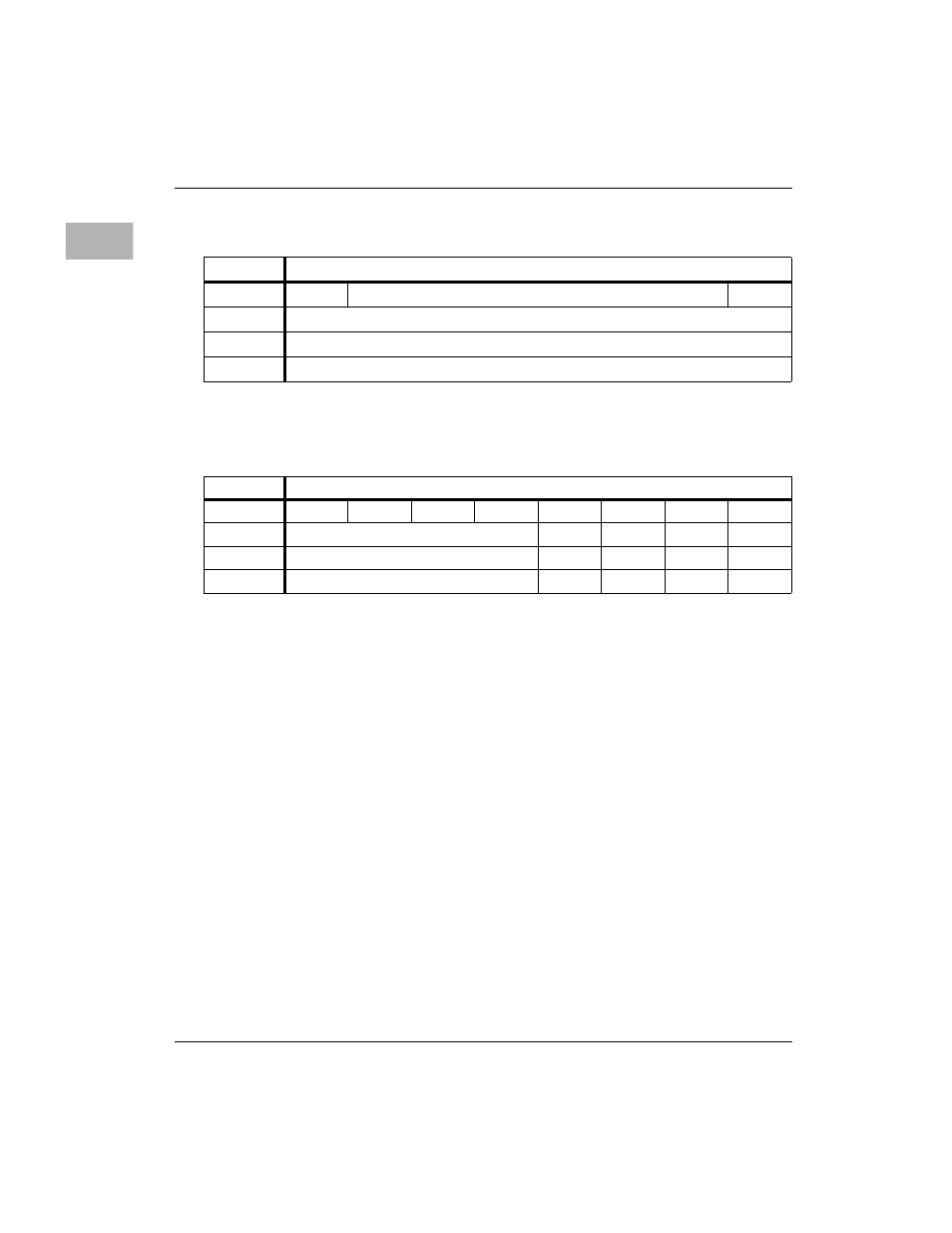

VMEbus Interrupter Vector Register

This register controls the VMEbus interrupter vector.

MPU Status and DMA Interrupt Count Register

This is the MPU status register and DMAC interrupt counter.

MLOB

When this bit is set, the MPU received a TEA and the

status indicated off-board. This bit is cleared by writing a

1 to the MCLR bit in this register.

MLPE

When this bit is set, the MPU received a TEA and the

status indicated a parity error during a DRAM data

transfer. This bit is cleared by writing a 1 to the MCLR bit

in this register.

MLBE

When this bit is set, the MPU received a TEA and no

additional status was provided. This bit is cleared by

writing a 1 to the MCLR bit in this register.

MCLR

Writing a 1 to this bit clears the MPU status bits 7, 8, 9,

and 10 (MLTO, MLOB, MLPE, and MLBE) in this

register.

ADR/SIZ

$FFF40048 (8 bits of 32)

BIT

23

. . .

16

NAME

Interrupter Vector

OPER

R/W

RESET

$0F PS

ADR/SIZ

$FFF40048 (8 bits of 32)

BIT

15

14

13

12

11

10

9

8

NAME

DMAIC

MCLR

MLBE

MLPE

MLOB

OPER

R

C

R

R

R

RESET

0 PS

0 PS

0 PS

0 PS

0 PS