Interrupt level register 4 (bits 07), Vector base register, Interrupt level register 4 (bits 0-7) -95 – Motorola MVME1X7P User Manual

Page 185

LCSR Programming Model

http://www.motorola.com/computer/literature

2-95

2

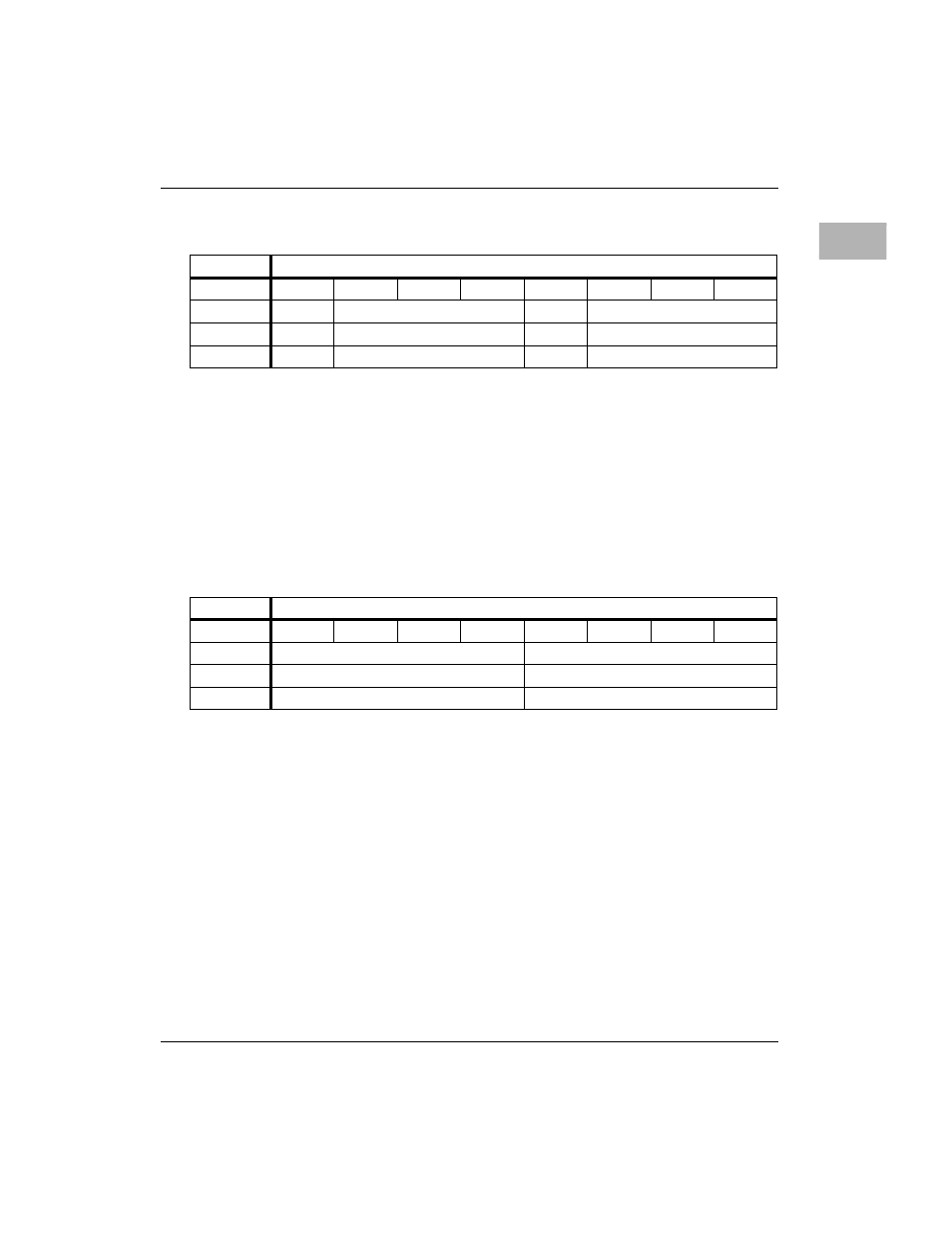

Interrupt Level Register 4 (bits 0-7)

This register is used to define the level of the VMEbus level 1 (IRQ1)

interrupt and the VMEbus level 2 (IRQ2) interrupt. The IRQ1 and IRQ2

interrupts may be mapped to any local bus interrupt level.

VIRQ1 LEVEL

These bits define the level of the VMEbus IRQ1 interrupt.

VIRQ2 LEVEL

These bits define the level of the VMEbus IRQ2 interrupt.

Vector Base Register

This register is used to define the interrupt base vectors.

VBR 1

These bits define the interrupt base vector 1.

VBR 0

These bits define the interrupt base vector 0.

Note

, Local Bus Interrupter Summary, for

further information.

A suggested setting for the VMEchip2 Vector Base register

is: VBR0 = 6, VBR1 = 7 (i.e., setting the Vector Base register

at address $FFF40088 to $67xxxxxx). This produces a

Vector Base0 of $60 corresponding to the “X” in

,

and a Vector Base1 of $70 corresponding to the “Y” in

ADR/SIZ

$FFF40084 (8 bits [6 used] of 32)

BIT

7

6

5

4

3

2

1

0

NAME

VIRQ2

VIRQ1 LEVEL

OPER

R/W

R/W

RESET

0 PSL

0 PSL

ADR/SIZ

$FFF40088 (8 bits of 32)

BIT

31

30

29

28

27

26

25

24

NAME

VBR 0

VBR 1

OPER

R/W

R/W

RESET

0 PSL

0 PSL