Lanc bus error interrupt control register, Lanc bus error interrupt control register -36 – Motorola MVME1X7P User Manual

Page 234

3-36

Computer Group Literature Center Web Site

PCCchip2

3

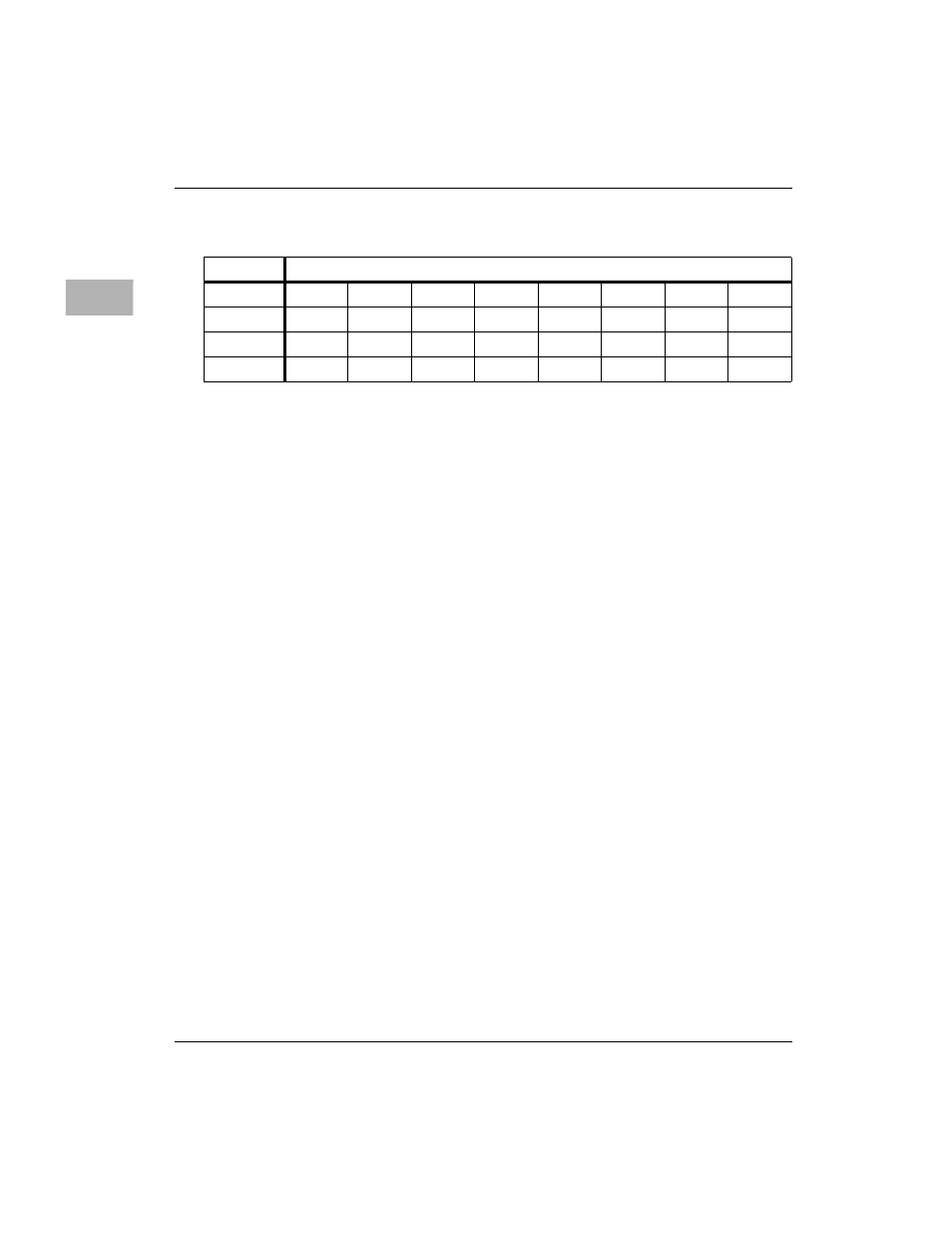

LANC Bus Error Interrupt Control Register

IL2-IL0

Interrupt Request Level. These three bits select the

interrupt level. Level 0 does not generate an interrupt.

ICLR

Writing a logic 1 into this bit clears the INT status bit.

This bit is always read as zero.

IEN

Interrupt Enable. When this bit is high, the interrupt is

enabled. The interrupt is disabled when this bit is low.

IRQ

Interrupt Status. When this bit is high, a LANC Bus Error

interrupt is being generated at the level programmed in

IL2-IL0 (if nonzero).

SC1-SC0

Snoop Control. These control bits determine the value that

the PCCchip2 drives onto the local MC68040 bus SC1

and SC0 pins, when the 82596CA (LANC) performs

DMA accesses.

During LANC DMA, if bit SC0 is 0 Local Bus pin SC0 is

low, and when bit SC0 is 1, pin SC0 is high. The same

relationship holds true for bit and pin SC1. See the

M68040 user’s manual for details on how it uses the

Snoop Control signals.

Note

On the MVME177P, which uses only SC1, the SC0 bit must be 0.

ADR/SIZ

$FFF4202B (8 bits)

BIT

7

6

5

4

3

2

1

0

NAME

SC1

SC0

INT

IEN

ICLR

IL2

IL1

IL0

OPER

R/W

R/W

R

R/W

C

R/W

R/W

R/W

RESET

0 PL

0 PL

0 PL

0 PL

0 PL

0 PL

0 PL

0 PL