Vmebus interrupter control register, Vmebus interrupter control register -61 – Motorola MVME1X7P User Manual

Page 151

LCSR Programming Model

http://www.motorola.com/computer/literature

2-61

2

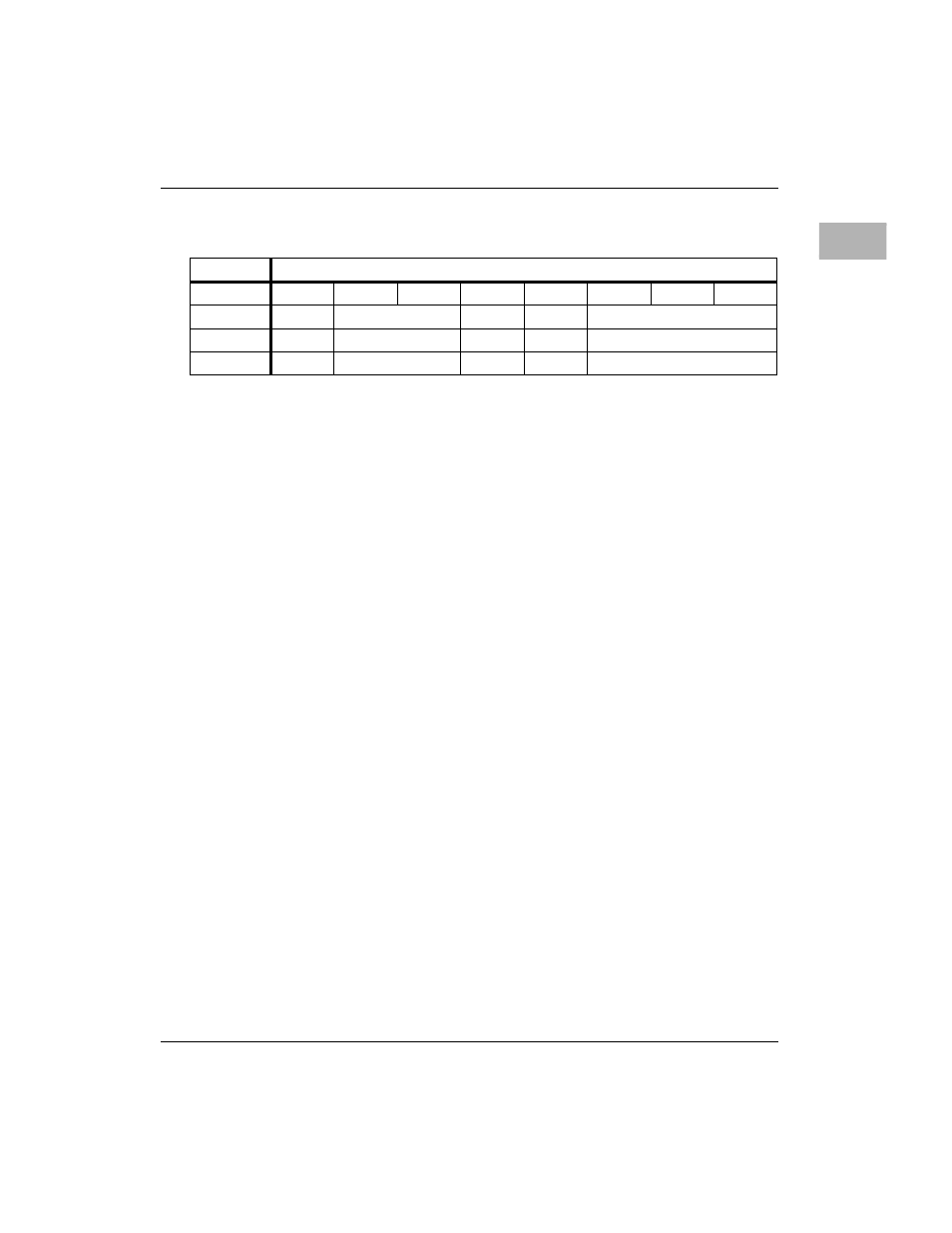

VMEbus Interrupter Control Register

This register controls the VMEbus interrupter.

IRQL

These bits define the level of the VMEbus interrupt

generated by the VMEchip2. A VMEbus interrupt is

generated by writing the desired level to these bits. These

bits always read 0 and writing 0 to these bits has no effect.

IRQS

This bit is the IRQ status bit. When this bit is high, the

VMEbus interrupt has not been acknowledged. When this

bit is low, the VMEbus interrupt has been acknowledged.

This is a read-only status bit.

IRQC

This bit is the VMEbus interrupt clear bit. When this bit is

set high, the VMEbus interrupt is removed. This feature is

only used when the IRQ1 broadcast mode is used. Normal

VMEbus interrupts should never be cleared. This bit

always reads 0; writing a 0 to it has no effect.

IRQ1S

These bits control the function of the IRQ1 signal line on

the VMEbus:

0

The IRQ1 signal from the interrupter is

connected to the VMEbus IRQ1 signal line.

1

The output from tick timer 1 is connected to

the VMEbus IRQ1 signal line.

2

The IRQ1 signal from the interrupter is

connected to the VMEbus IRQ1 signal line.

3

The output from tick timer 2 is connected to

the VMEbus IRQ1 signal line.

ADR/SIZ

$FFF40048 (8 bits [7 used] of 32)

BIT

31

30

29

28

27

26

25

24

NAME

IRQ1S

IRQC

IRQS

IRQL

OPER

R/W

S

R

S

RESET

0 PS

0 PS

0 PS

0 PS