Dmac control register 2 (bits 815), Dmac control register 2 (bits 8-15) -57 – Motorola MVME1X7P User Manual

Page 147

LCSR Programming Model

http://www.motorola.com/computer/literature

2-57

2

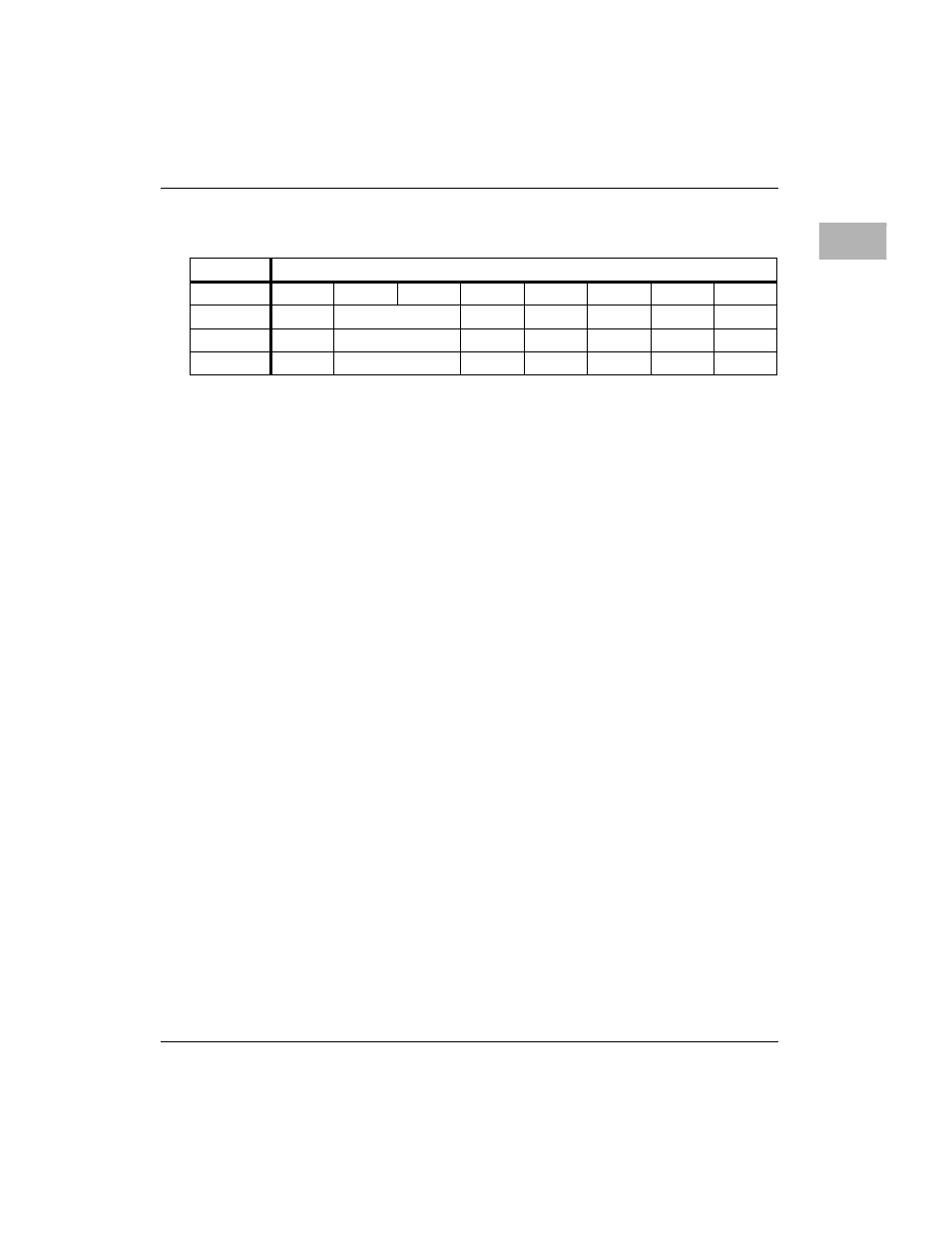

DMAC Control Register 2 (bits 8-15)

This portion of the control register is loaded by the processor or by the

DMAC when it loads the command word from the command packet.

Because this register is loaded from the command packet in command

chaining mode, the descriptions here also apply to the control word in the

command packet.

D16

When this bit is high, the DMAC executes D16 cycles on

the VMEbus. When this bit is low, the DMAC executes

D32/D64 cycles on the VMEbus.

TVME

This bit defines the direction in which the DMAC

transfers data. When this bit is high, data is transferred to

the VMEbus. When it is low, data is transferred to the

local bus.

LINC

When this bit is high, the local bus address counter is

incremented during DMA transfers. When this bit is low,

the counter is not incremented. This bit should normally

be set high. In special situations such as transferring data

to or from a FIFO, it may be desirable to not increment the

counter.

VINC

When this bit is high, the VMEbus address counter is

incremented during DMA transfers. When this bit is low,

the counter is not incremented. This bit should normally

be set high. In special situations such as transferring data

to or from a FIFO, it may be desirable to not increment the

counter.

ADR/SIZ

$FFF40034 (8 bits [7 USED] of 32)

BIT

15

14

13

12

11

10

9

8

NAME

INTE

SNP

VINC

LINC

TVME

D16

OPER

R/W

R/W

R/W

R/W

R/W

R/W

RESET

0 PS

0 PS

0 PS

0 PS

0 PS

0 PS