Scc error status and interrupt control registers, Scc error status register, Scc error status register -27 – Motorola MVME1X7P User Manual

Page 225: 3scc error status and interrupt control registers

Programming Model

http://www.motorola.com/computer/literature

3-27

3

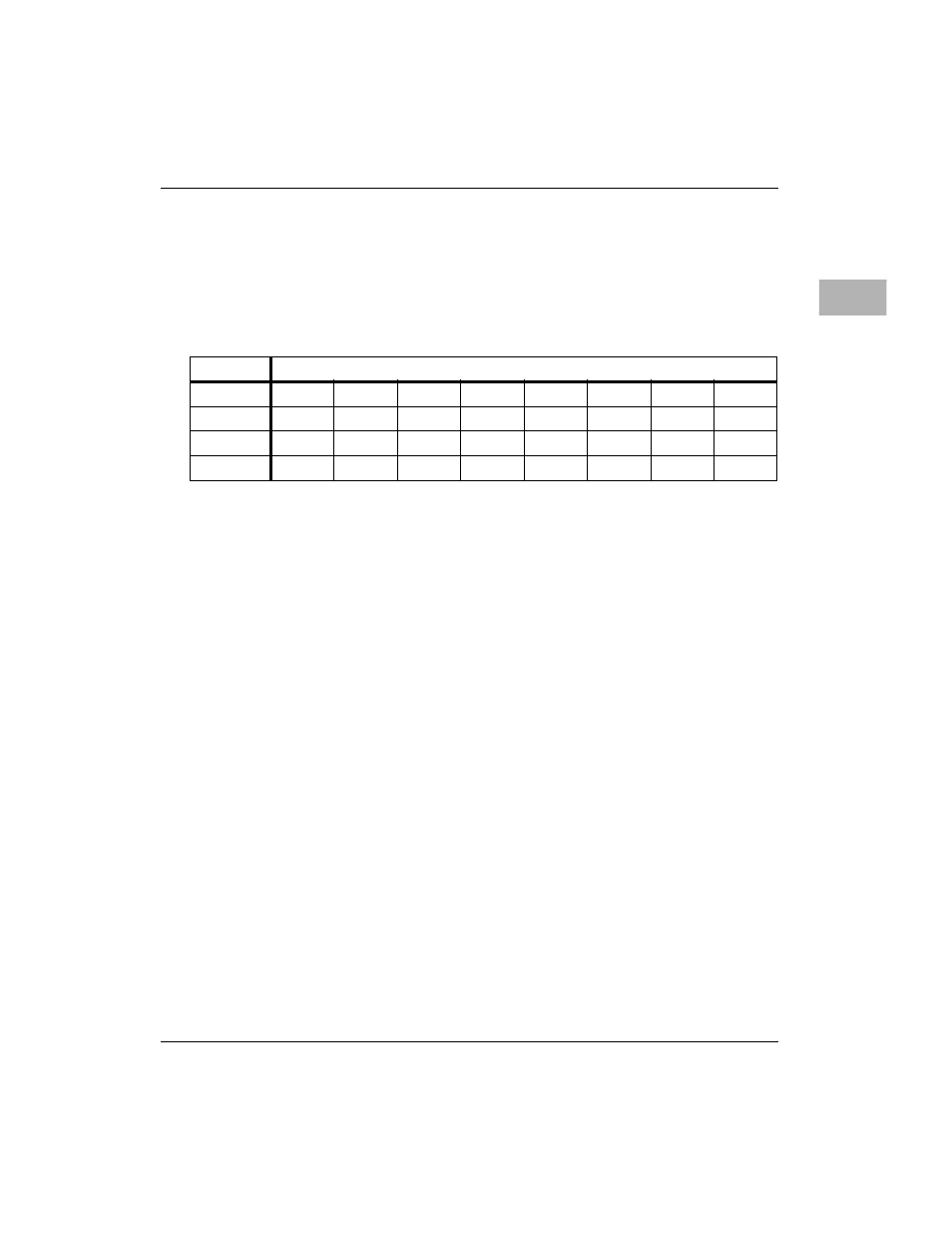

SCC Error Status and Interrupt Control Registers

This section provides addresses and bit level descriptions of the SCC

interrupt control registers and status registers.

SCC Error Status Register

SCLR

Writing a 1 to this bit clears bits 25 through 28 (LTO,

EXT, PRTY, and RTRY). Reading this bit always yields

0.

LTO,EXT,

These bits indicate the status of the last Local Bus

PRTY,RTRY error condition encountered by the SCC while performing

DMA accesses to the Local Bus. A Local Bus error

condition is flagged by the assertion of TEA*. When the

SCC receives TEA* if the source of the error is local-

time-out, then LTO is set and EXT, PRTY, and RTRY are

cleared. If the source of the TEA* is due to an error in

going to the VMEbus, then EXT is set and the other three

status bits are cleared. If the source of the error is DRAM

parity check error, then PRTY is set and the other three

status bits are cleared. If the source of the TEA* is

because a retry was needed, then RTRY is set and the

other three status bits are cleared. If the source of the error

is none of the above conditions, then all four bits are

cleared. Writing a 1 to bit 24 (SCLR) also clears all four

bits.

ADR/SIZ

$FFF4201C (8 bits)

BIT

31

30

29

28

27

26

25

24

NAME

RTRY

PRTY

EXT

LTO

SCLR

OPER

R

R

R

R

W/R-0

RESET

0

0

0

0 PL

0 PL

0 PL

0 PL

0