Motorola DSP96002 User Manual

Page 99

MOTOROLA

DSP96002 USER’S MANUAL

7 - 13

If

—

H

–

R is used and the host processor reads RX or writes TX when the DSP96002 is in the Stop state,

then

—

H

–

R will only be deasserted after exiting the Stop state. .

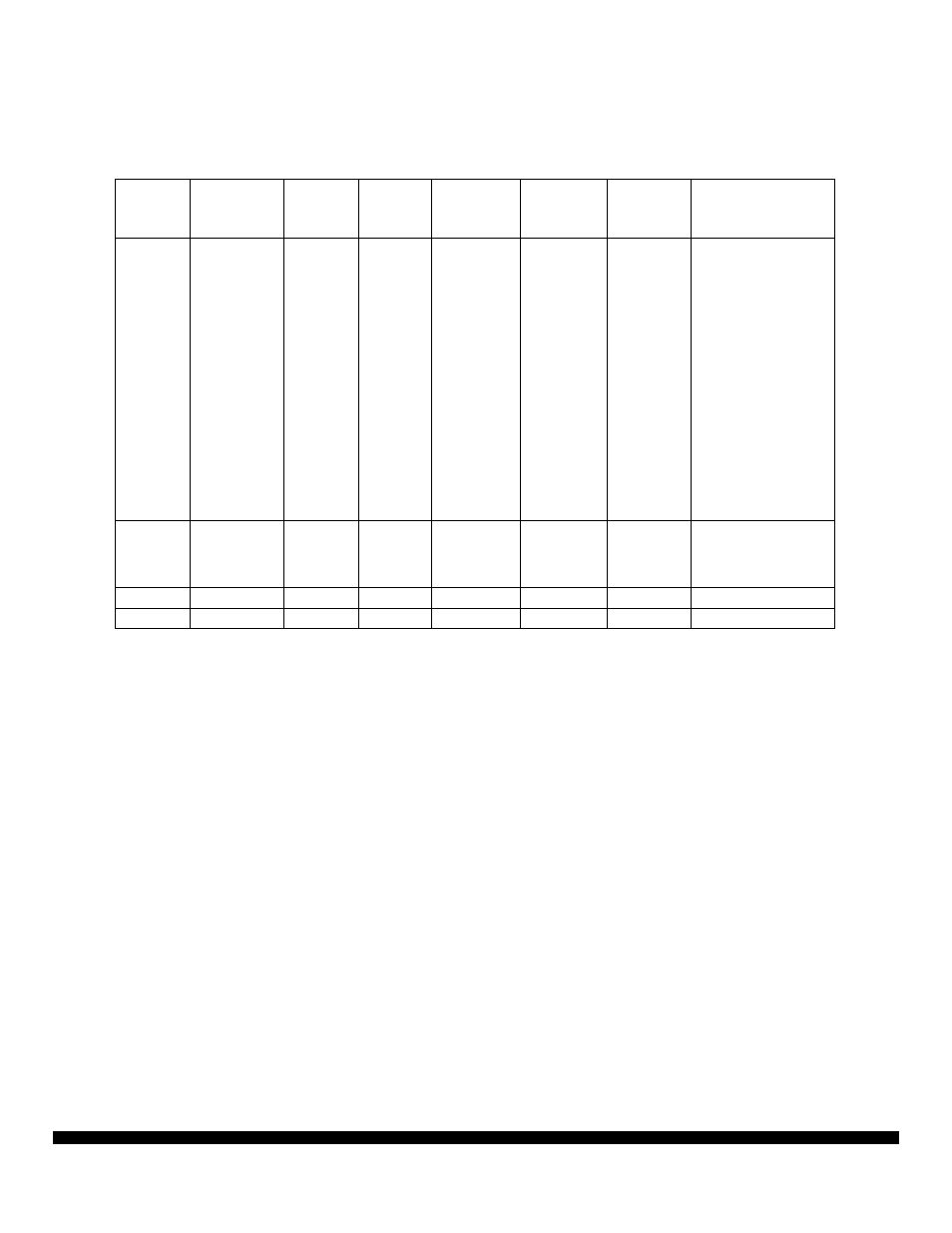

Register

Register

HW/SW

HOST

INIT

INIT

INIT

Comments

Name

Contents Reset

Reset

TREQ=1

TREQ=0

TREQ=1

RREQ=0

RREQ=1

RREQ=1

ICS

HMRC

0 0 0 - 0

HRST

1 1 - - -

DMAE

0 - - - -

HF3-HF2

0 - - - -

HF1-HF0

0 - - - -

HREQ

0 Note

1

1 Note

2

1

INIT

0 - 0 0 0

TYEQ

0 - - - -

TREQ

0 - 1 0 1

RREQ

0 - 0 1 1

TRDY

1 1 1 - 1

TXDE

1 1 1 - 1

RXDF

0 0 - 0 0

CVR

HC

0

-

-

-

-

HV7-HV0

$0E

- - - -

port

A

$0F

- - - -

port

B

IVR

IV7-IV0

$0F

- - - -

SEM

SEM(15-0)

$0000

- - - -

Notes:

1. HREQ = TYEQ + TREQ

2. HREQ = (TYEQ & TRDY) + (TREQ & TXDE)

Symbols:

HW - Hardware Reset caused by asserting the external pin

—

R

—

E

—

S

—

E

–

T.

SW - Software Reset caused by executing the RESET instruction.

HOST - Host Personal Reset caused when HRES=1.

INIT - Host Personal Reset caused when INIT=1.

"1" - The bit is set.

"0" - The bit is cleared.

"-" - The bit is not affected.

"+" - Logical OR operation.

"&" - Logical AND operation.

Figure 7-7. Host Interface Reset - Host Processor Side