Motorola DSP96002 User Manual

Page 88

7 - 2

DSP96002 USER’S MANUAL

MOTOROLA

7.2.1.1 BCRx Wait Control Fields (Bits 0-15)

The BCRx Wait Control fields specify the number of wait states to be inserted in the bus cycle for an external

X memory, Y memory, program memory or I/O access. Four bits are available in the control register for each

type of external memory access. Each 4 bit field can specify up to 15 wait states. The Wait Control fields

are set to ’$F’ (15 wait states) during hardware reset. See Section 2 for a description of the interaction be-

tween the wait states determined by the BCR and wait states generated due to the

—

T

–

A pin. Neither soft-

ware reset, nor page circuit personal reset, affect BCRx.

7.2.1.2

BCRx Page Size (P3–P0) Bits 16-19

These bits define the page size for page fault operation. P3-P0 are set to ’1010’ by hardware reset. See

Section 7.2.2 on Page Circuit Operation.

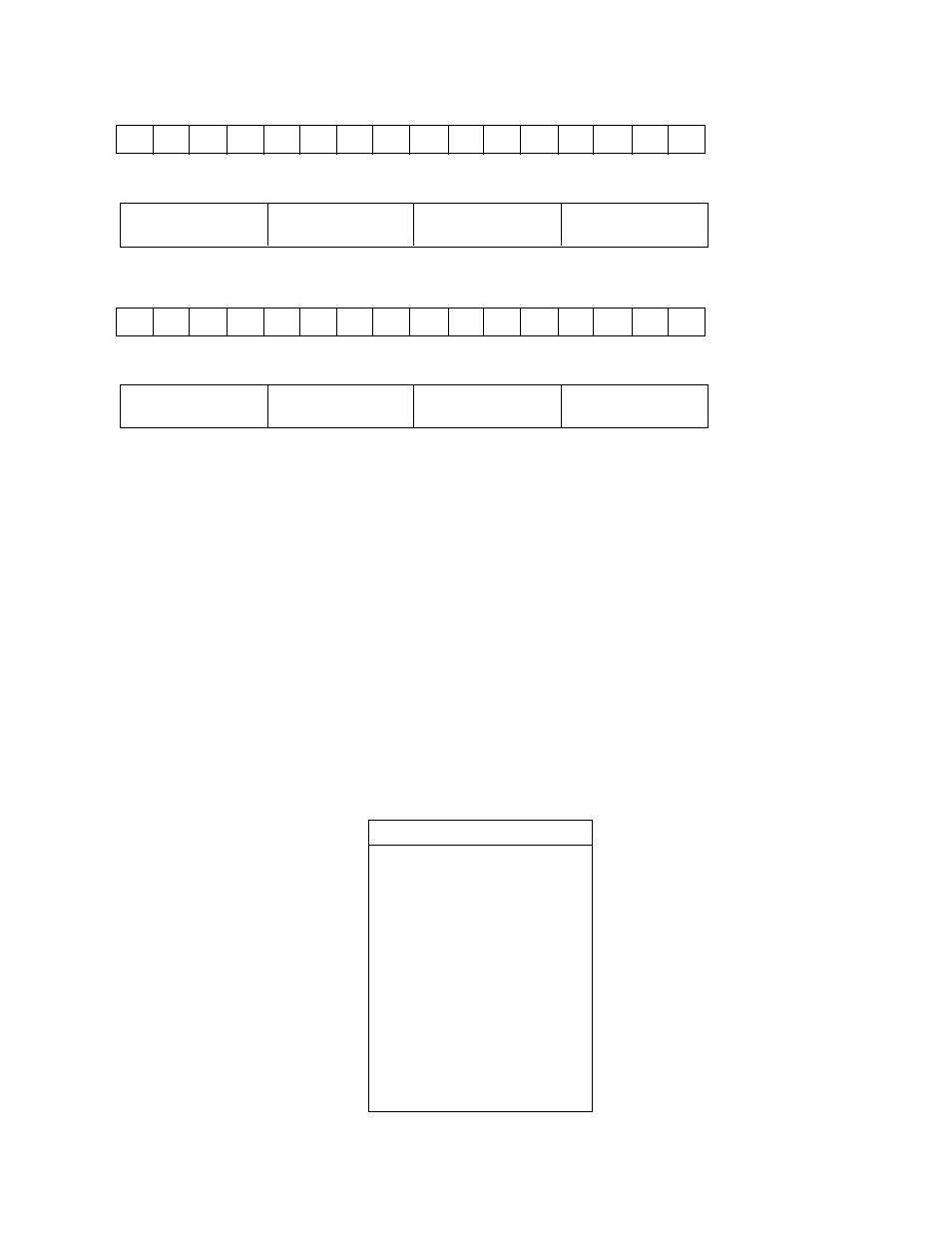

31

16

15

12 11

8 7

4 3

0

RH

LH

BS

XE

YE

PE SF1 SF0 MF NS

**

**

P3

P2

P1

P0

Port A

Bus Control

Register (BCRA)

X:$FFFFFFFE

External X Memory

Wait Control

External Y Memory

Wait Control

External Prog Memory

Wait Control

External I/O Memory

Wait Control

15

12 11

8 7

4 3

0

31

16

RH

LH

BS

XE

YE

PE SF1 SF0 MF NS

**

**

P3

P2

P1

P0

Port B

Bus Control

Register (BCRB)

X:$FFFFFFFD

External X Memory

Wait Control

External Y Memory

Wait Control

External Prog Memory

Wait Control

External I/O Memory

Wait Control

** – reserved, read as zero, should be written with zero for future compatibility.

Figure 7-1. DSP96002 Bus Control Registers (BCRA and BCRB)

P3-P0 Page Size

0000 1

0001 2

0010 4

0011 8

0100 16

0101 32

0110 64

0111 128

1000 256

1001 512

1010 1,024 (Reset value)

1011 2,048

1000 4,096

1101 8,192

1110 16,384

1111 32,768