Motorola DSP96002 User Manual

Page 102

7 - 16

DSP96002 USER’S MANUAL

MOTOROLA

7.4.6 Host Transmit Data Register and HMRC Clear (HTXC) - DSP96002 Side

The Host Transmit register and HMRC Clear (HTXC) is used for DSP96002 to host processor data trans-

fers in conjunction with "TX register write (address) and X/Y/P Memory Read (data) Interrupt" host func-

tions. The HTXC register is viewed as a 32-bit write-only register by the DSP96002. Writing the HTXC

register clears HTDE, HPRP, HXRP and HYRP. The HTXC register is transferred as 32-bit data to the

Receive Register RX if both the HTDE bit and the Receive Data Full RXDF status bit are cleared. This

transfer operation sets RXDF and HTDE, and clears HMRC (See Section 7.4.21.10).

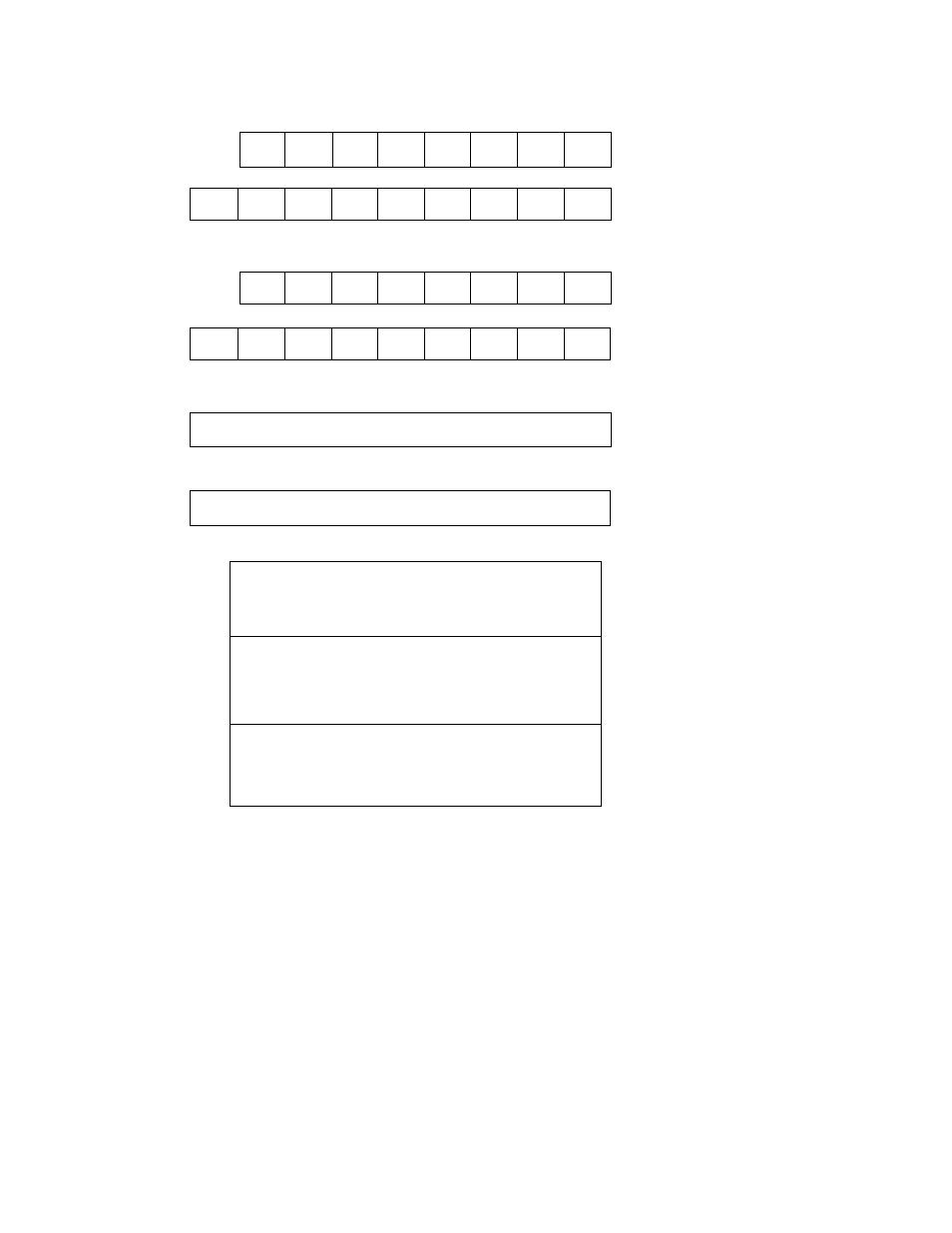

7 6 5 4 3 2 1 0

** ** HRES HF3 HF2 HCIE HTIE HRIE

READ/WRITE

HOST CONTROL

31 .... 14 13 12 11 10 9 8

REGISTER

** ** ** HYWE HYRE HXWE HXRE HPWE HPRE

HCR

7 6 5 4 3 2 1 0

HDMA ** ** HF1 HF0 HCP HTDE HRDF

READ-ONLY

HOST STATUS

31 .... 14 13 12 11 10 9 8

REGISTER

** ** ** HYWP HYRP HXWP HXRP HPWP HPRP

HSR

31 0

READ-ONLY

32-bit receive data register HOST RECEIVE

DATA REGISTER

HRX

31 0

WRITE-ONLY

32-bit transmit data register HOST TRANSMIT

DATA REGISTER

HTX or HTXC

HOST INTERFACE DSP96002 ADDRESS MAP

ADDR (HEX) DSP96002 DSP96002

READ WRITE

X:$FFFFFFEC HCRA HCRA

X:$FFFFFFED HSRA ---- PORT A

X:$FFFFFFEE ---- HTXCA

X:$FFFFFFEF HRXA HTXA

X:$FFFFFFE4 HCRB HCRB

X:$FFFFFFE5 HSRB ---- PORT B

X:$FFFFFFE6 ---- HTXCB

X:$FFFFFFE7 HRXB HTXB

** - reserved, read as zero, should be written with zero

for future compatibility.

Figure 7-10. HI - DSP96002 Programming Model