Motorola DSP96002 User Manual

Page 748

MOTOROLA

DSP96002 USER’S MANUAL

C-25

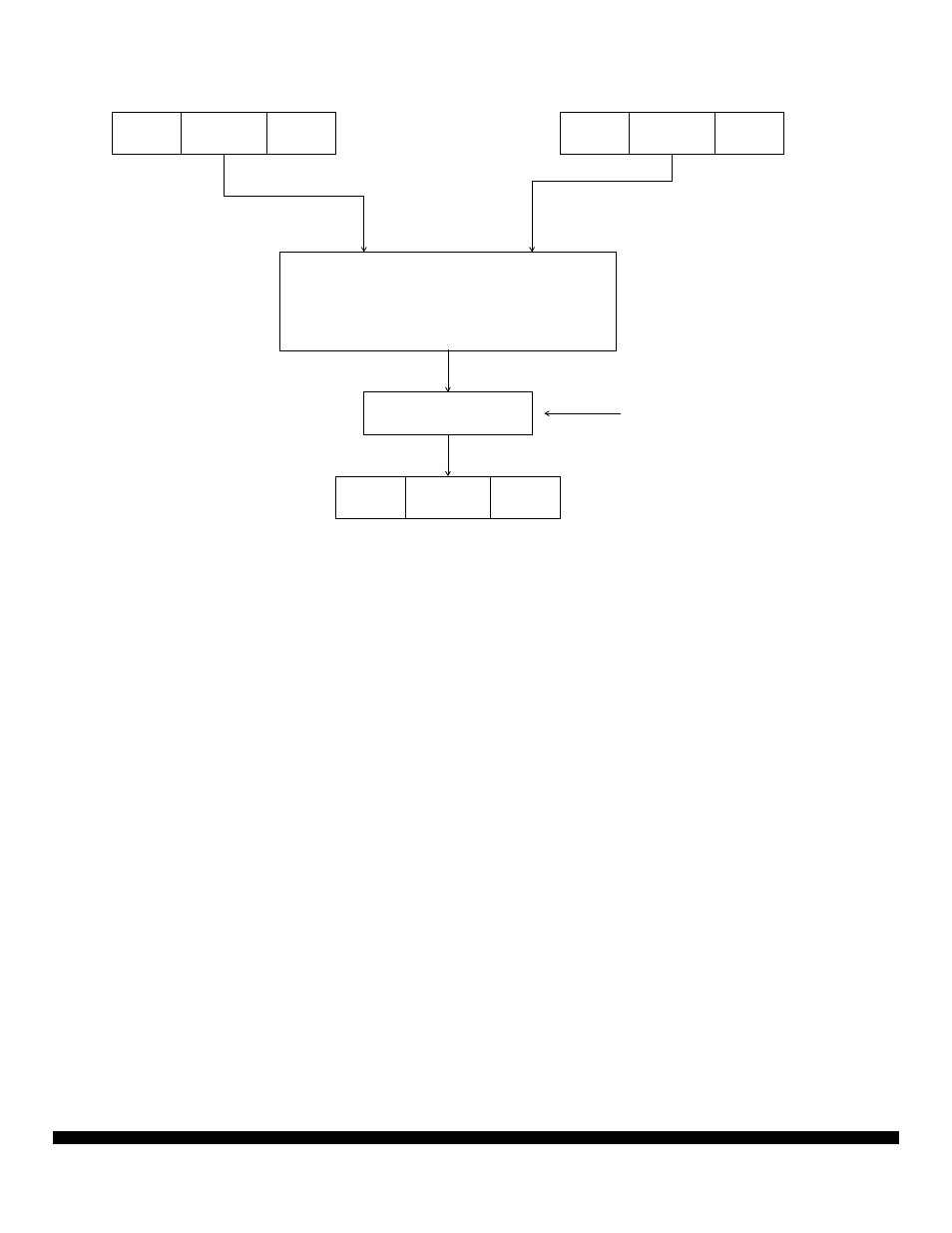

M1

M2

MD

D

32 Bits

64 Bits

32 Bits

32 Bits

Multiplier Array

Round

Rounding mode is determined

by rounding bits in the MR.

C.1.5.4

Special Function Unit

The special function unit (SFU) consists of a logic unit and a divide and square root unit. The logic unit is

further described under the fixed point (integer) operations.

The divide and square root unit supports execution of the divide and square root algorithms. These algo-

rithms are iterative, and require an initial approximation or "seed". These seeds are generated in the SFU.

The FSEEDD and FSEEDR instructions provide an initial approximation to 1/x and sqrt(1/x), as is described

in Appendix A.

C.1.5.5

Controller and Arbitrator Unit

The controller and arbitrator (CA) unit supplies control signals to the processing units of the data ALU and

register file, and is responsible for the full implementation of the IEEE standard. Its operation is determined

by the flush-to-zero (FZ) bit in the status register (SR), which determines whether or not denormalized num-

bers are treated as defined by the standard. In the flush-to-zero mode, all denormalized input operands are

treated as zeros (although their original contents are preserved), and denormalized results are set equal to

zero ("flushed-to-zero"). In the flush-to-zero mode, no additional cycles are required for the normalization of

denormalized numbers as they are treated as zeros. In the IEEE mode, the standard for treatment of de-

normalized numbers is correctly and fully implemented. However, operations on denormalized numbers can

not be performed in a single instruction cycle, except for operations done in the floating point adder when

the operand is a denormalized number in SEP. The controller and arbitrator is responsible for providing the

correct sequence that deals with such situations.

When denormalized numbers are detected as input operands in IEEE mode, the CA unit adds one extra

cycle for entering the IEEE mode procedure. Next, one additional cycle is added for each denormalized in-