Motorola DSP96002 User Manual

Page 94

7 - 8

DSP96002 USER’S MANUAL

MOTOROLA

—

T

–

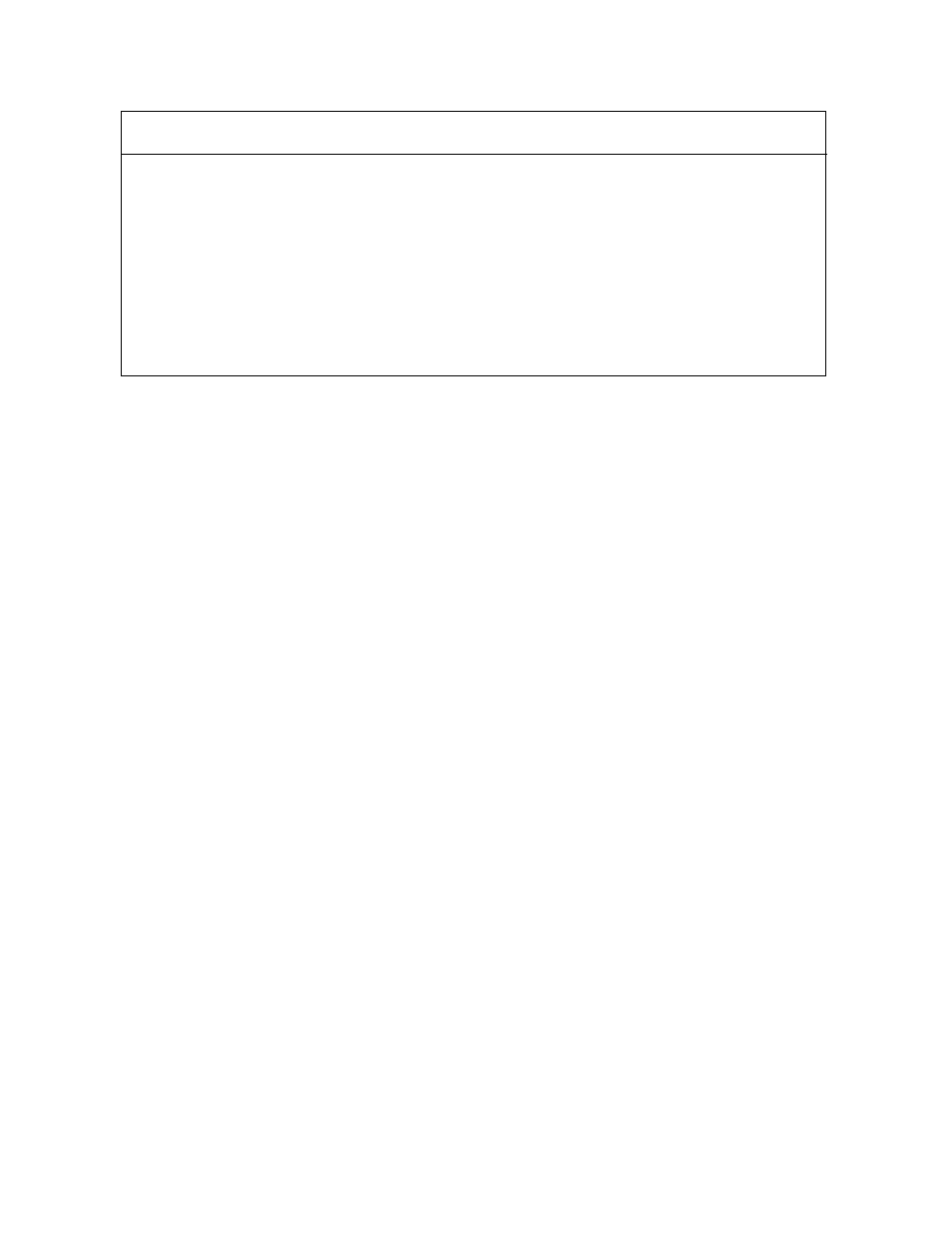

T Pin Activity for Current Bus Cycle Latched for

PE XE YE P Space X Space Y Space P Space X Space Y Space

0 0 0 Deasserted Deasserted Deasserted No No No

0 0 1 Deasserted Deasserted Active No No Yes

0 1 0 Deasserted Active Deasserted No Yes No

0 1 1 Deasserted Active Active No Yes Yes

1 0 0 Active Deasserted Deasserted Yes No No

1 0 1 Active Deasserted Active Yes No Yes

1 1 0 Active Active Deasserted Yes Yes No

1 1 1 Active Active Active Yes Yes Yes

Figure 7-5. Memory Space Enables Encoding

7.2.2.2

Refresh Faults

There is no internal support for refresh timers, refresh address counters or refresh faults which should deas-

sert

—

T

–

T. The page circuit assumes that refresh does not exist and therefore

—

T

–

T must be interpreted

by the external memory controller based on its knowledge of refresh timing and external bus activity. The

use of multiple processors with the same external DRAM/VRAM indicates that the memory controller is the

best place to enforce refresh priorities. With the variety of refresh techniques based on the expected mem-

ory activity, the external memory controller state machine is the best place to have global control over re-

fresh timing and arbitration caused by multiple access conflicts. At the end of each external bus cycle, the

external memory controller should determine if it should begin a refresh cycle. If yes, it will disable the trans-

fer acknowledge

—

T

–

A signal to ensure that the DSP96002 waits if it begins an external access. Once the

refresh is completed, the external memory controller must remember to ignore the

—

T

–

T signal for the next

memory cycle so that a fast access mode is not used. The external state machine should cancel (ignores)

the effect of the

—

T

–

T signal in the next external bus cycle after any hardware refresh operation. Note that

if fast interrupts are used to implement a software refresh, refresh looks like a memory read cycle so no

special treatment of

—

T

–

T is needed.

7.2.2.3

—

R

—

A

–

S,

—

C

—

A

–

S and SC Timeout Faults

Since DRAM/VRAM devices are dynamic, there are maximum limits on the

—

R

—

A

–

S and

—

C

—

A

–

S low

time which must be observed. To effectively use the fast access modes with the DSP96002, the external

state machine must keep

—

R

—

A

–

S asserted between bus cycles for page, nibble and static column

modes.

—

C

—

A

–

S must remain asserted between bus cycles for static column mode only. However, if no

external access occurs after the external state machine is ready for a fast access mode, there is a possibility

that

—

R

—

A

–

S or

—

C

—

A

–

S may "timeout". This is because the idle memory state must be "

—

R

—

A

–

S ac-

tive" to use the fast access modes with the DSP96002 non-burst, random address bus cycles. The

DSP96002 does not provide any internal support for

—

R

—

A

–

S or

—

C

—

A

–

S timeouts. The external state