Motorola DSP96002 User Manual

Page 763

MOTOROLA

DSP96002 USER’S MANUAL

D-11

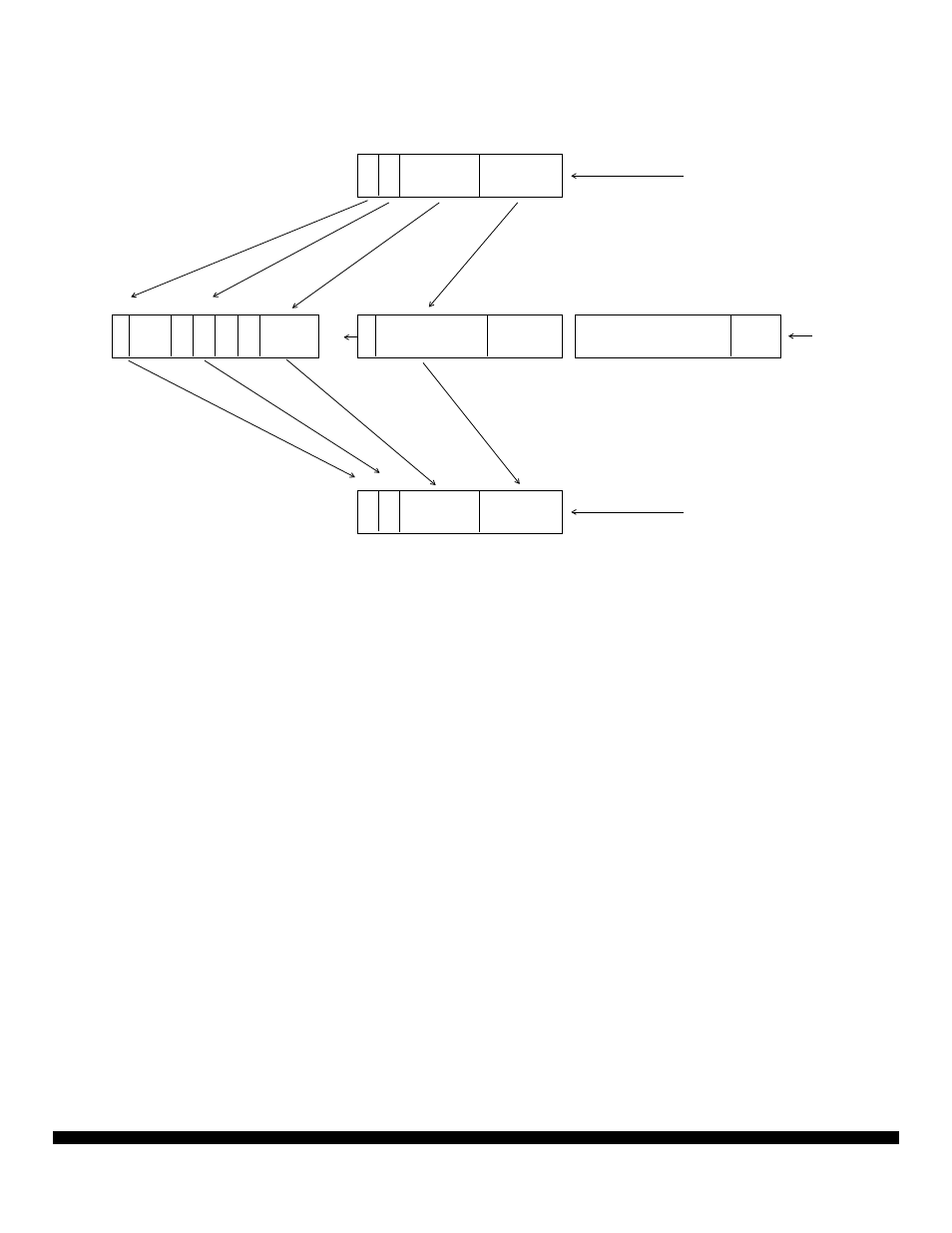

formats to/from the DP storage format in the data ALUs register file. The conversion is depicted in Figure

D-10 and is done in a transparent fashion.

When moving SP numbers into the data ALU, the 52-bit fraction of the DP internal format is written with the

23-bit fraction of the source in its most significant bits, and the implicit integer bit is made explicit. The re-

maining bits of the fraction are set equal to zero. If the number in question is denormalized (exponent = e

min

and the first bit of the mantissa = 0), the U tag is set. In the non-IEEE "flush to zero" mode (indicated by the

FZ bit in the Status Register), the number is considered zero when used as an operand for floating-point

operations, although the contents of the register are not changed. In the IEEE mode, the number is "cor-

rected" when used as an operand for floating point calculations, at the expense of extra cycles introduced

for normalization.

The 8-bit exponent of the SP source is translated into an 11-bit exponent by copying the 7 least significant

bits of the source exponent into the seven least significant bits of the destination. The most significant bit of

the 8-bit exponent of the source is copied to the most significant bit of the exponent of the destination. The

31 30 29

0

Fraction

23 22

E

95 94 74 73 72 71

64

63 62

32 31

11 10

0

S

E

(3)

Fraction

i

*

X or Y Data Memory

i = 1 when normalized

i = 0 when unnormalized

(2)

Dn

Figure D-10a. Automatic Format Conversion – Single Precision

S

40 39

31 30 29

0

Fraction

23 22

E

X or Y Data Memory

S

† †

†

†

(1)

Notes: * –

† – When NaN bits 71, 72, 73 = 1

When not NaN Bit 74

↔

Bit 30

Bits 73, 72, 71 are complement

of Bit 74.

(1) – Bits 32-39 are nonzero when the register

contains a SEP floating point result or a

DP floating point number.

Bits 32-39 are zero when the register

contains a SP floating point number.

(2) – Bits 11-31 are only nonzero when the

register contains a DP floating point

number.

(3) – Bits 0-10 are always zero when

representing a floating point number.