Motorola DSP96002 User Manual

Page 41

4 - 2

DSP96002 USER’S MANUAL

MOTOROLA

M7

M6

M5

M4

M3

M2

M1

M0

R7

R6

R5

R4

R3

R2

R1

R0

ADDRESS GENERATION UNIT

N7

N6

N5

N4

N3

N2

N1

N0

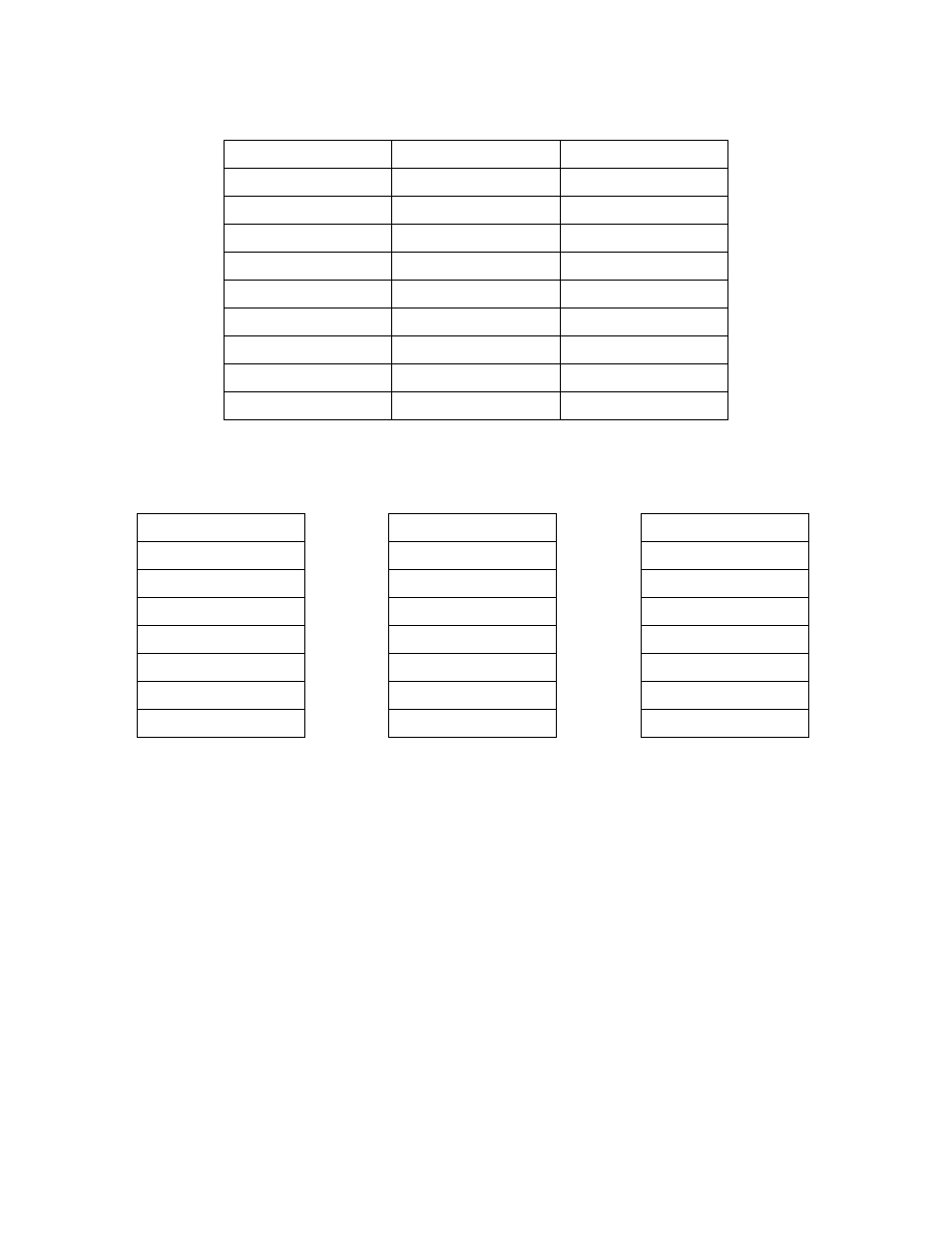

Figure 4-2. DSP96002 Programming Model –

Data ALU and Address Generation Unit

95

0

31

0

31

0 31 0

31 0

31

0

31

0

D9.H

D8.H

D7.H

D6.H

D5.H

D4.H

D3.H

D2.H

D1.H

D0.H

D9.M

D8.M

D7.M

D6.M

D5.M

D4.M

D3.M

D2.M

D1.M

D0.M

D9.L

D8.L

D7.L

D6.L

D5.L

D4.L

D3.L

D2.L

D1.L

D0.L

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

DATA ALU

4.2

DATA ALU REGISTER FILE (D0-D9)

The ten registers, D0-D9, are 96-bits wide and may be treated as thirty independent 32-bit registers or as

ten 96-bit floating-point registers. Each 96-bit register is divided into three sub-registers: high, middle and

low. Each sub-registers may be addressed individually by specifying the register number and the name of

the sub-registers (e.g. D0.H, D0.M, D0.L). The low sub-register is used as source and destination for the

integer operations. When writing to or reading from a sub-register no format conversion is performed.

The 96-bit registers Dn (n=0,...,9) are developed by the concatenation of Dn.H:Dn.M:Dn.L forming a float-

ing-point data register. The data representation in a floating-point data register is always in an internal rep-

resentation of the IEEE double precision format. When writing a register with a single or double precision