Motorola DSP96002 User Manual

Page 5

2 - 2

DSP96002 USER’S MANUAL

MOTOROLA

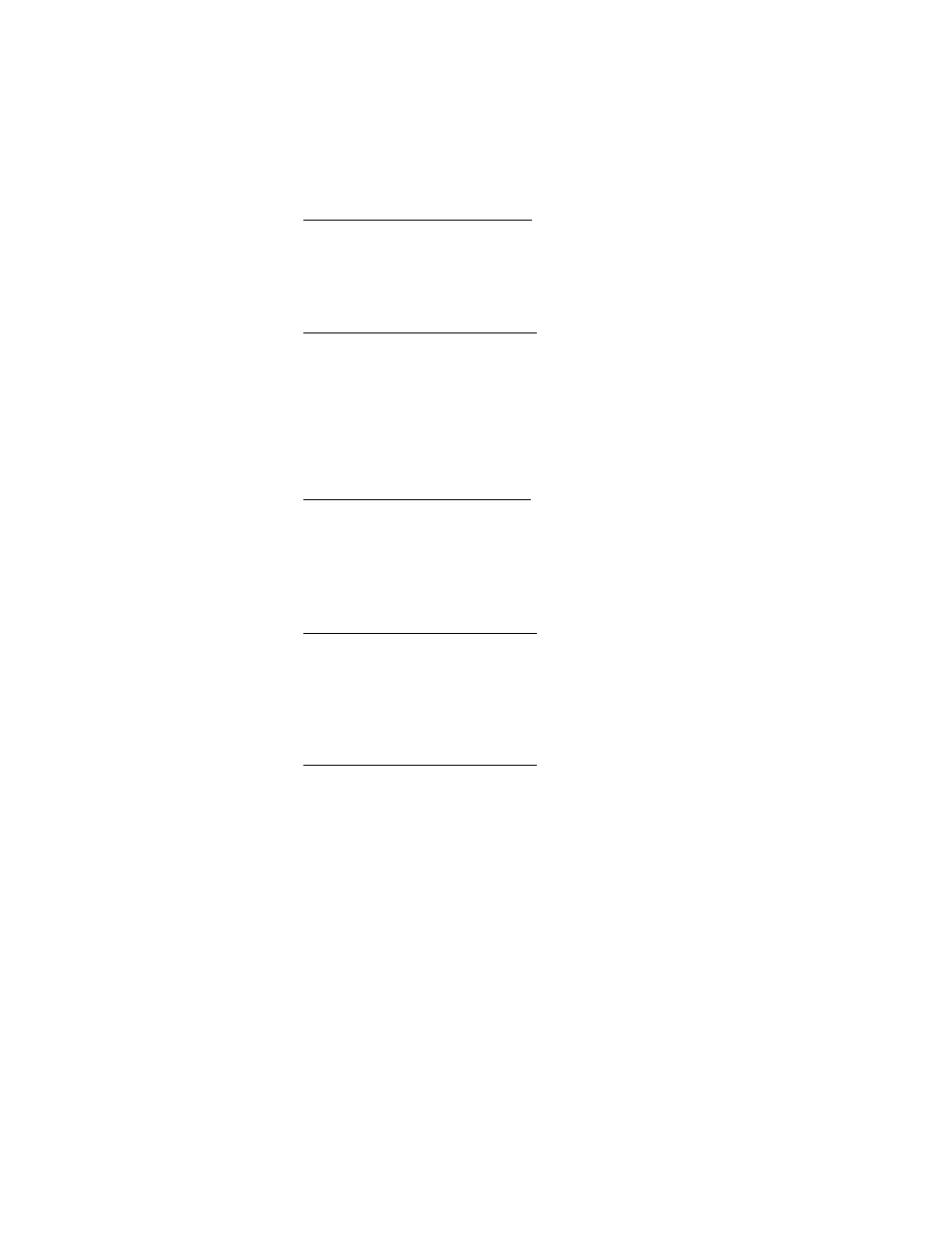

CPU Pins

Pins

Reset and IRQs

4

Clock Input

1

OnCE Port

4

CPU Spare

1

Quiet Power

4

Quiet Ground

4

CPU Subtotal

18

Power/Ground Planes

Pins

Package Noisy Power Plane

2

Package Noisy Ground Plane

5

Package Quiet Power Plane

1

Package Quiet Ground Plane

1

Power/Ground Plane Subtotal

9

Each Port Both Ports

Port A/B

Pins

Pins

Data Bus

32

64

Address Bus

32

64

Data Power

2

4

Data Ground

4

8

Address Power

2

4

Address Ground

4

8

Addr/Data Subtotal

76

152

Each Port Both Ports

Port A/B

Pins

Pins

Bus Control Signals

17

34

Bus Control Spare

2

4

Bus Control Power

1

2

Bus Control Ground

2

4

Control Subtotal

22

44

Pinout Summary

Pins

CPU Pins

18

Package Power/Ground Planes

9

Port A/B Pins

Data and Address

152

Bus Control

44

TOTALS

223

Figure 2-1. DSP96002 Functional Group Pin Allocation

MODB/

—

I

—

R

—

Q

–

B(Mode Select B/External Interrupt Request B) - active low input, internally synchronized

to the input clock (CLK). MODB/

—

I

—

R

—

Q

–

B selects the initial chip operating mode dur-

ing hardware reset and becomes a level sensitive or negative edge triggered, maskable

interrupt request input during normal instruction processing. MODA, MODB and MODC

select one of 8 initial chip operating modes, latched into the operating mode register

(OMR) when the

—

R

—

E

—

S

—

E

–

T pin is deasserted. If

—

I

—

R

—

Q

–

B is asserted syn-

chronous to the input clock (CLK), multiple processors can be resynchronized using the

WAIT instruction and asserting

—

I

—

R

—

Q

–

B to exit the wait state.

MODC/

—

I

—

R

—

Q

–

C(Mode Select C/External Interrupt Request C) - active low input, internally synchronized

to the input clock (CLK). MODC/

—

I

—

R

—

Q

–

C selects the initial chip operating mode dur-